USB On-The-Go IP

Welcome to the ultimate USB On-The-Go IP hub! Explore our vast directory of USB On-The-Go IP

All offers in

USB On-The-Go IP

Filter

Compare

48

USB On-The-Go IP

from

9

vendors

(1

-

10)

-

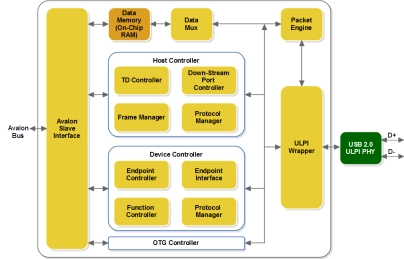

USB 2.0 On-The-Go (USB20OTG)

- The USB 2.0 On-The-Go (OTG) IP Core is a 32-bit Avalon interface compliant core and supports ULPI interface.

- It supports both USB Host and USB Device peripheral functionality.

- While acting as USB Host, it supports High Speed (HS), Full Speed (FS) and Low Speed (LS) modes.

- While acting as USB Device peripheral, it supports High Speed (HS) and Full Speed (FS) modes.

-

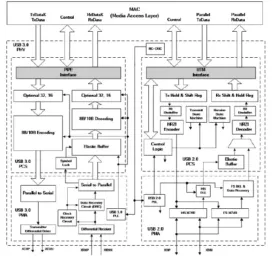

USB2.0 On-The-Go IP Core

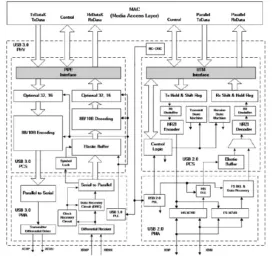

- The host/device (OTG) solutions include a variety of host device configurations around a single USB port.

- OTG is a supplement to the USB 2.0 specification mainly introduced to provide a low‐cost connectivity for portable devices such as mobile phones.

-

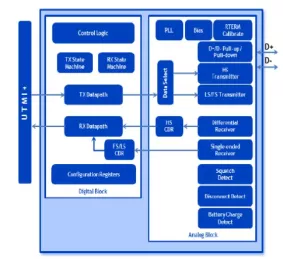

USB 2.0 Host/Device Transceiver With On-The-Go (OTG)

- Fully compliant with latest USB 2.0

- Innovative technique to recover clock from 480 Mbps data.

- High frequency PLL.

- Advanced High-Speed Transmitter and Receiver.

-

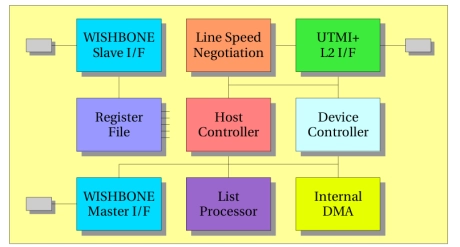

USB 2.0 On-The-Go IP Core, Compliance Certified

- A ‘Dual-Role’ USB 2.0 On-The-Go IP Core that operates as both an USB 2.0 peripheral or as an USB 2.0 OTG host in a point-to-point communications with another USB device.

- The USB OTG IP Core is fully USB 2.0 and USB 2.0 On-The-Go Supplement compliant.

-

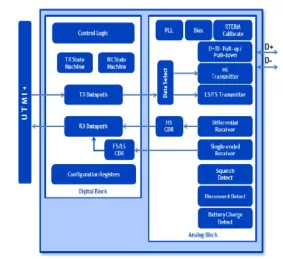

USB 2.0 PHY IP, Silicon Proven in SMIC 40LL

- Compliant with USB2.0 and USB1.1 specification

- Compliant with UTMI Specification Version level 3.

- Supports HS (480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

- All required terminations, including 1.5Kohm pullup on DP and DM, and 15Kohm pull-down on DP and DM are internal to chip

-

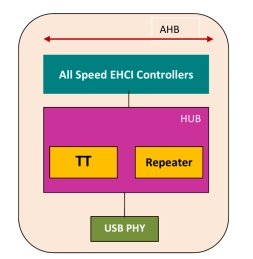

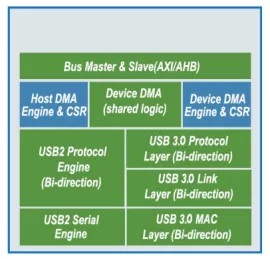

USB 3.0 OTG High / Full / Low- Speed Dual Role IP Core

- Support SW controlled host/device role switching.

- Support Superspeed, Highspeed and Fullspeed

- Support Control, Bulk, Interrupt and Isochronous Transfer Types

- Support U1/U2/U3 power saving modes for USB 3.x port

-

USB 2.0 PHY IP, Silicon Proven in SMIC 55LL

- Compliant with USB2.0 and USB1.1 specification

- Compliant with UTMI Specification Version level 3.

- Supports HS (480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

- All required terminations, including 1.5Kohm pullup on DP and DM, and 15Kohm pull-down on DP and DM are internal to chip

-

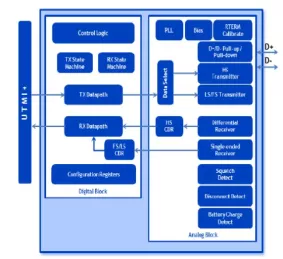

USB 2.0 PHY IP, Silicon Proven in UMC 40LP

- Compliant with USB2.0 and USB1.1 specification

- Compliant with UTMI Specification Version level 3.

- Supports HS(480Mbps)/FS(12Mbps) /LS(1.5Mbps) modes

- All required terminations, including 1.5Kohm pullup on DP and DM, and 15Kohm pull-down on DP and DM are internal to chip

-

USB 3.0 PHY IP, Silicon Proven in UMC 40SP

- Compliant with Universal Serial Bus 3.0 Specification

- Supports 2.5GT/s and 5.0GT/s serial data transmission rate

- Compliant with PIPE 3.0

- Compliant with Universal Serial Bus 2.0 Specification

-

USB 3.0 PHY IP, Silicon Proven in TSMC 28HPC+

- Compliant with Universal Serial Bus 3.0 Specification

- Supports 2.5GT/s and 5.0GT/s serial data transmission rate

- Compliant with PIPE 3.0

- Compliant with Universal Serial Bus 2.0 Specification