Interface IP Cores for TSMC

Welcome to the ultimate

Interface IP Cores

for

TSMC

hub! Explore our vast directory of

Interface IP Cores

for

TSMC

All offers in

Interface IP Cores

for

TSMC

Filter

Compare

70

Interface IP Cores

for

TSMC

from

4

vendors

(1

-

10)

Filter:

- 3nm

-

PCIe 6.0 PHY, TSMC N3A x4 1.2V, North/South (vertical) poly orientation for Automotive, ASIL B Random, AEC-Q100 Grade 2

- Supports the latest features of PCIe 6.x and CXL 3.x specifications

- Supports PAM-4 signaling and up to x16 lane configurations with bifurcation

- Delivers more power efficiency across channels with unique DSP algorithms

- Enables near zero link downtime with patent-pending diagnostic features

-

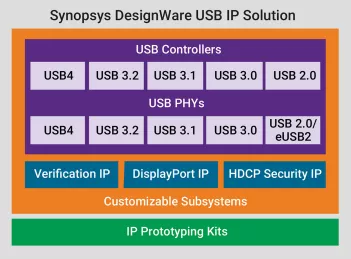

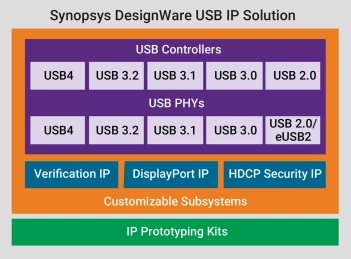

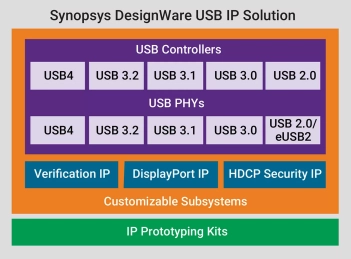

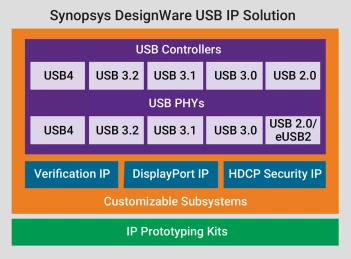

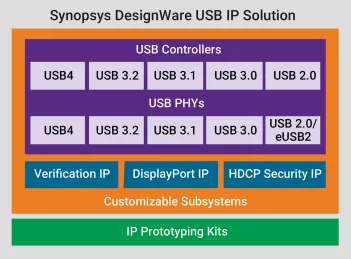

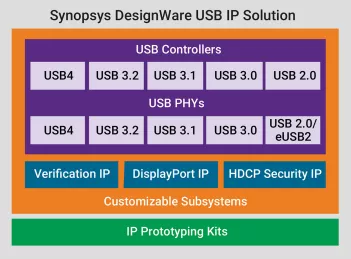

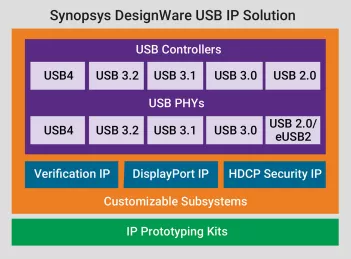

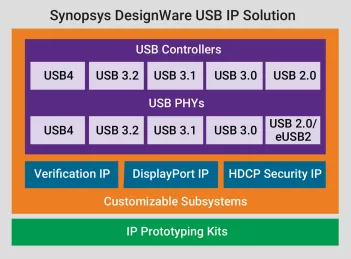

USB 4.0 V2 PHY - 4TX/2RX, TSMC N3P , North/South Poly Orientation

- Supports 40 Gbps, 20 Gbps, 10 Gbps, and 5 Gbps data rates

- Supports 480 Mbps, 12 Mbps, and 1.5 Mbps data rates

- x1 and x2 configurations (USB 3.2 and USB 3.1 PHY only)

- Low active and standby power

- Small area for low silicon cost

-

USB4 PHY - TSMC N4P 1.2V, North/South Poly Orientation

- Supports 40 Gbps, 20 Gbps, 10 Gbps, and 5 Gbps data rates

- Supports 480 Mbps, 12 Mbps, and 1.5 Mbps data rates

- x1 and x2 configurations (USB 3.2 and USB 3.1 PHY only)

- Low active and standby power

- Small area for low silicon cost

-

USB4 PHY - TSMC N3E 1.2V, North/South Poly Orientation

- Supports 40 Gbps, 20 Gbps, 10 Gbps, and 5 Gbps data rates

- Supports 480 Mbps, 12 Mbps, and 1.5 Mbps data rates

- x1 and x2 configurations (USB 3.2 and USB 3.1 PHY only)

- Low active and standby power

- Small area for low silicon cost

-

USB4 PHY - TSMC N5 1.2V, North/South Poly Orientation

- Supports 40 Gbps, 20 Gbps, 10 Gbps, and 5 Gbps data rates

- Supports 480 Mbps, 12 Mbps, and 1.5 Mbps data rates

- x1 and x2 configurations (USB 3.2 and USB 3.1 PHY only)

- Low active and standby power

-

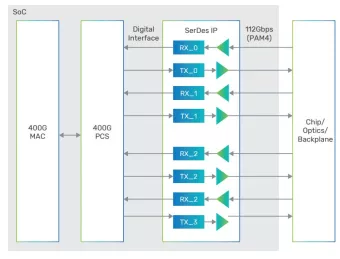

224G-LR SerDes PHY enables 1.6T and 800G networks

- Optimized Performance, Power and Area with Design Agility

- Supports full-duplex 1.25 to 225Gbps data rates

- Enables 1.6T, 800G, 400G, and 200G Ethernet with a PHY + Controller solution

- Supports evolving IEEE 802.3 and OIF-CEI-224G standard electrical specifications

- Meets the performance requirements of chip-to-module (VSR), chip-to-chip (MR), and copper/backplane (LR) interconnects

-

USB 2.0 femtoPHY - TSMC N3P 1.2V x1, North/South (vertical) poly orientation

- Ported to over 50 different processes and configurations ranging from 65-nm to 14/16-nm FinFET

- Supports the USB 2.0 protocol and data rate (480 Mbps)

- Supports the USB Type-C specification

- USB femtoPHY, USB nanoPHY and USB picoPHY offer a tunability feature that allows quick, post-silicon adjustments that occur due to process variations, or unexpected chip and board parasitic, without modifying the existing design

-

eUSB 2.0 PHY - TSMC N3P x1, North/South (vertical) poly orientation

- Designed for 7nm processes and below

- Supports the USB 2.0 protocol and High Speed, Full Speed, and Low Speed data rates

- eUSB2 PHYs supports USB 2.0, 3.0, 3.1 and 3.2 Device, Host and Dual Role configurations

-

eUSB 2.0 PHY - TSMC N3E x1, North/South (vertical) poly orientation

- Designed for 7nm processes and below

- Supports the USB 2.0 protocol and High Speed, Full Speed, and Low Speed data rates

- eUSB2 PHYs supports USB 2.0, 3.0, 3.1 and 3.2 Device, Host and Dual Role configurations

-

USB-C 3.2 DP/TX PHY for TSMC N3P, North/South poly orientation

- USB-IF certified Synopsys USB 3.2 solution

- VESA certified Synopsys DisplayPort 1.4 Tx solution

- Industry’s only USB Type-C IP solution consisting of USB-C 3.2/DisplayPort 1.4 TX PHYs, USB-C 3.2/DisplayPort 1.4 TX controllers with HDCP 2.2 and HDCP 2.2 content protection, verification IP, and IP subsystems

- Solution supports USB Type-C, SuperSpeed USB 3.2 at 20 Gbps, SuperSpeed USB 3.1 at 10 Gbps, SuperSpeed USB 3.0 at 5 Gbps and High-Speed USB (USB 2.0) as well as DisplayPort 1.4 TX supporting RBR, HBR1, HBR2 and HBR3 bitrates