PLL IP for TSMC

Welcome to the ultimate

PLL IP

for

TSMC

hub! Explore our vast directory of

PLL IP

for

TSMC

All offers in

PLL IP

for

TSMC

Filter

Compare

37

PLL IP

for

TSMC

from

5

vendors

(1

-

10)

Filter:

- 6nm

-

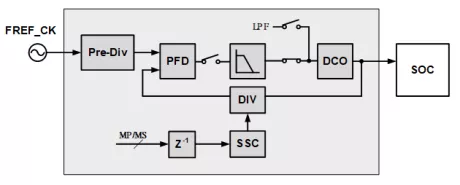

All Digital Fractional-N RF Frequency Synthesizer PLL in TSMC N6/N7

- Fractional Multiplication with frequencies up to 8GHz

- Extremely low jitter (sub 300fs RMS)

- Small size (< 0.05 sq mm)

- Low Power (< 7mW)

-

Low Power All Digital Fractional-N PLL in TSMC N6/N7

- Low power, suitable for IoT applications

- Good jitter, suitable for clocking digital logic.

- Extremely small die area (< 0.005 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 1.5GHz

-

Low Power All Digital Fractional-N PLL in Samsung 8LPP

- Low power, suitable for IoT applications

- Good jitter, suitable for clocking digital logic.

- Extremely small die area (< 0.005 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 1.5GHz

-

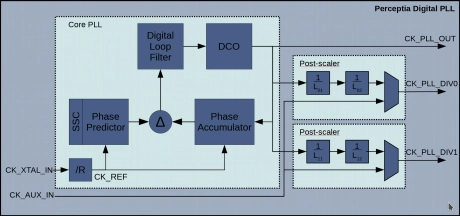

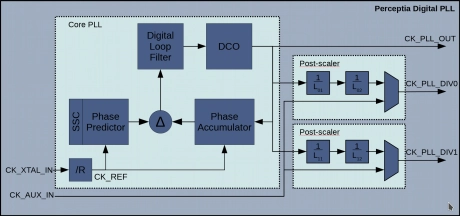

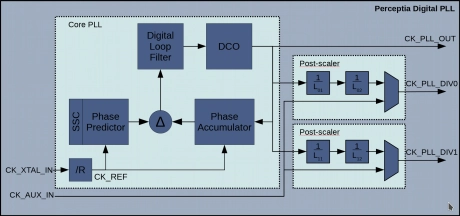

Low Power FracN/SSCG PLL on TSMC CLN6FF

- Electrically Programmable PLL with Fractional-N divide and Spread Spectrum Clock Generation

- Wide Ranges of Input and Output Frequency for diverse clocking needs

- Very fine precision: near 1 part per billion resolution

- Fully integrated 32-bit datapath (8-bit integer plus 24-bit fractional)

-

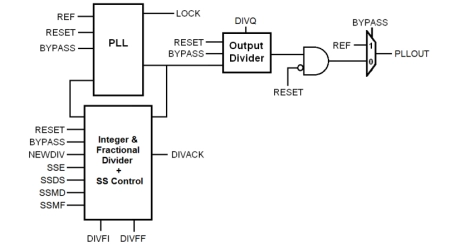

4.8GHz low jitter fractional-N, Digital PLL, TSMC N6, 0.75V, N/S orientation

- Pure core voltage design

- Compact IP size (< 0.013mm²) and low power consumption (1.1mW @ 3GHz)

- Compatible with commonly used crystal oscillator frequencies

- Good power noise immunity for period jitter (< ±15%/V)

-

Wide Range Programmable Integer PLL on TSMC CLN6FF

- Electrically Programmable PLL for multiple applications

- Wide Ranges of Input and Output Frequency for diverse clocking needs

- Implemented with Analog Bits’ proprietary architecture

- Low power consumption

-

Wide Range Multi-Output PLL on TSMC CLN6FF

- Electrically Programmable PLL for multiple applications

- Wide Ranges of Input and Output Frequency (including multiple outputs) for diverse clocking needs

- Implemented with Analog Bits’ proprietary architecture

- Low power consumption

-

PCIe Gen4/5/6 Class Low Jitter LC PLL on TSMC CLN6FF

- High performance design emphasis for meeting low jitter requirements in PCIe Gen3/4/5 applications

- Implemented with Analog Bits’ proprietary LC architecture

- Low power consumption

- Spread Spectrum Clock Generation (SSCG) and tracking capability

-

High Speed Multi-Phase PLL on TSMC CLN6FF

- Electrically Programmable PLL for multiple applications

- Wide Ranges of Output Frequency for diverse clocking needs

- Implemented with Analog Bits’ proprietary architecture

- Low power consumption

-

High Performance 20GHz PLL on TSMC CLN6FF

- Electrically Programmable PLL for multiple applications

- Implemented with Analog Bits’ proprietary architecture

- Low power consumption

- Integrated LDO to reduce deterministic jitter