PCI IP for GLOBALFOUNDRIES

Welcome to the ultimate

PCI IP

for

GLOBALFOUNDRIES

hub! Explore our vast directory of

PCI IP

for

GLOBALFOUNDRIES

All offers in

PCI IP

for

GLOBALFOUNDRIES

Filter

Compare

15

PCI IP

for

GLOBALFOUNDRIES

from

4

vendors

(1

-

10)

-

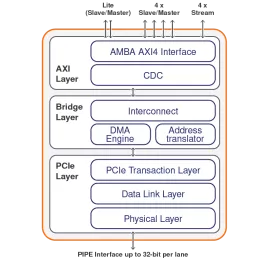

PCIe 3.1 Controller with AXI

- Compliant with the PCI Express 3.1/3.0, and PIPE (16- and 32-bit) specifications

- Compliant with PCI-SIG Single-Root I/O Virtualization (SR-IOV) Specification

- Supports Endpoint, Root-Port, Dual-mode configurations

- Supports x16, x8, x4, x2, x1 at 8 GT/s, 5 GT/s, 2.5 GT/s speeds

- Supports AER, ECRC, ECC, MSI, MSI-X, Multi-function, P2P, crosslink, and other optional features

- Supports many ECNs including LTR, L1 PM substates, etc.

-

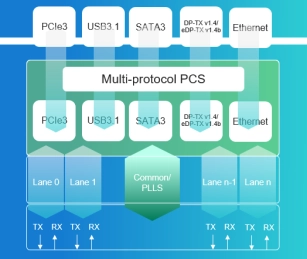

PHY for PCIe 3.1

- Supports PCIe 3.1, USB 3.1, DP-TX v1.4/eDP-TX v1.4b, SATA 3, 10G-KR and QSMII/SGMII

- Multi-protocol support for simultaneous independent links

- Supports SRIS and internal SSC generation

- Supports PCIe L1 sub-states

- Automatic calibration of on-chip termination resistors

- Supports internal and external clock sources with clock active detection

-

PCIe 2.0 PHY, GF 28SLP x4, East/West (horizontal) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 PHY, GF 28SLP x2, East/West (horizontal) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 PHY, GF 28SLP x1, East/West (horizontal) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 PHY, GF 22FDX x2, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 PHY, GF 12LP+ x2 North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 PHY, GF 12LP+ x1, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 PHY, GF 12LP x2, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 5.0 PHY, GF 12LP+ x1, North/South (vertical) poly orientation

- Supports all required features of the PCIe® 5.0, 4.0, 3.1, 2.1, 1.1, PIPE, and CXL 1.0, 1.1, and 2.0 specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- Multi-tap adaptive and programmable Continuous Time Linear Equalizer (CTLE) and Decision Feedback Equalization (DFE) supporting more than 36dB channel loss

- Adaptive receiver equalizer with programmable settings