IP for GLOBALFOUNDRIES

Welcome to the ultimate

IP

for

GLOBALFOUNDRIES

hub! Explore our vast directory of

IP

for

GLOBALFOUNDRIES

All offers in

IP

for

GLOBALFOUNDRIES

Filter

Compare

1,058

IP

for

GLOBALFOUNDRIES

from

61

vendors

(1

-

10)

-

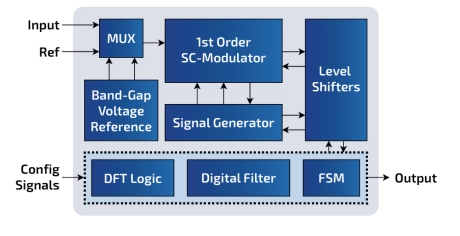

Voltage and Temperature Sensor with integrated ADC - GlobalFoundries® 22FDX®

- Voltage and temperature monitoring

- 3 single-ended voltage measurement inputs

- Operating temperature range: -40°C to 150°C

- Temperature measurement with accuracy up to 1°K ± 1°K change in temperature

-

Crystal Oscillator for a 32 kHz Crystal - GLOBALFOUNDRIES® 22FDX®

- Specific crystal: 32 kHz

- Supported series resistance: up to 100 kOhm

- Supported load capacitance: 3 pF to 12.5 pF

- Startup time: 59 ms (TT, 12 pF) depending on crystal and PCB

-

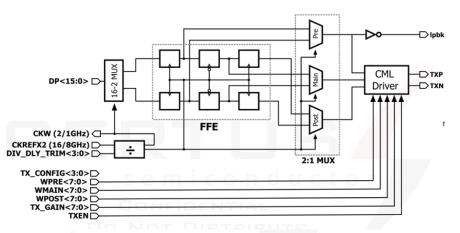

32Gbps SerDes PHY in GF 22nm

- This 32Gbps SerDes PHY is implemented in GlobalFoundries 22FDX CMOS technology and provides a high-performance, protocol-agnostic serial interface for advanced mixed-signal and high-speed digital SoCs.

- The PHY is architected as a modular design consisting of a low-jitter clock multiplier, a half-rate transmitter with digitally programmable feed-forward equalization, and a configurable CTLE-based receiver with digital clock-and-data recovery, supporting both 16 Gbps and 32 Gbps operation.

-

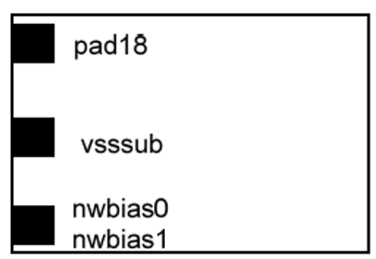

Stand-Alone ESD Cell in GF 28nm

- This ESD library is a silicon-proven set of discrete, pad-independent ESD clamps for GlobalFoundries 28nm technology.

- The library is designed to provide robust ESD protection for power domains and low-speed signals in advanced SoCs where traditional pad-based protection is insufficient or impractical.

-

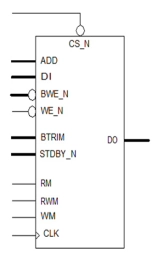

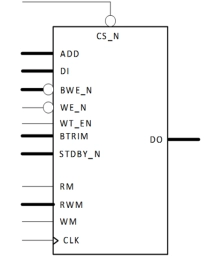

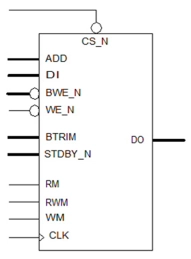

Single Port High-Speed Multi Bank SRAM Memory Compiler on GF 22FDX+

- Ultra-Low Leakage - GLOBALFOUNDRIES low-leakage 6T L110 bit cells with High Vt and low leakage periphery to ensure minimal leakage and high yield.

- Multi-Bank Architecture - Memory split into 1 to 4 banks for reduced bit line length and enhanced timing.

- Ultra Low Power Standby - Built-in source biasing trims standby current to a minimum for data retention.

-

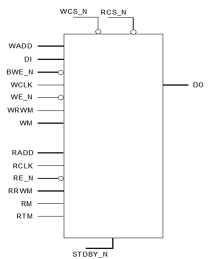

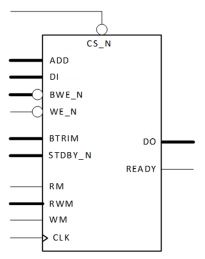

Dual Port Register File Compiler (1 Read-only port, 1 Write-only port) - GF 22FDX+

- Uses 8T-TP185SL bit cells.

- Isolated Supplies: Periphery and array power domains can be independently powered down in standby mode.

- Deep Sleep Standby Mode: Memory retains data at minimal power via internal biasing.

-

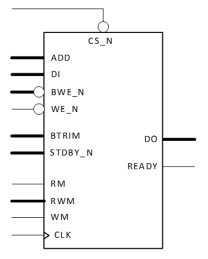

Single Port Low Leakage SRAM Memory Compiler on GF 22FDX+

- Ultra-Low Leakage: High VT (HVT) and low leakage (LLHVT) devices are used with source biasing to minimize standby currents while operating at low voltage

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage 6T (P110UL) bit cells to ensure high manufacturing yields

- Five Power Modes: High Performance, Low Leakage, Standby, Retention, and Power Off modes provide flexibility for power optimization

- Speed Grades: Three options to adjust the speed/leakage balance and optimize for high speed or low power operation

-

Single Port Low Leakage Register File Compiler - GF 22FDX+

- Ultra-Low Leakage: High VT (HVT) and low leakage HVT (LLHVT) devices used with source biasing to minimize standby currents while operating at low voltage.

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage 6T (L110) bit cells to ensure high manufacturing yields.

- Four Power Modes: Active, Standby, Retention, and Power Off modes provide flexibility for power optimization

-

Single Port Low Leakage SRAM Memory Compiler on GF 22FDX

- Ultra-Low Leakage: High VT (HVT) and low leakage (LLHVT) devices are used with source biasing to minimize standby currents while operating at low voltage

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage 6T (P110UL) bit cells to ensure high manufacturing yields

- Five Power Modes: High Performance, Low Leakage, Standby, Retention, and Power Off modes provide flexibility for power optimization

- Speed Grades: Three options to adjust the speed/leakage balance and optimize for high speed or low power operation

-

Single Port Low Leakage Register File Compiler - GF 22FDX+

- Ultra-Low Leakage: High VT (HVT) and low leakage HVT (LLHVT) devices used with source biasing to minimize standby currents while operating at low voltage

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage 6T (P110UL) bit cells to ensure high manufacturing yields

- Four Power Modes: Active, Standby, Retention, and Power Off modes provide flexibility for power optimization