Forward Error Correction IP

Welcome to the ultimate Forward Error Correction IP hub! Explore our vast directory of Forward Error Correction IP

All offers in

Forward Error Correction IP

Filter

Compare

86

Forward Error Correction IP

from

19

vendors

(1

-

10)

-

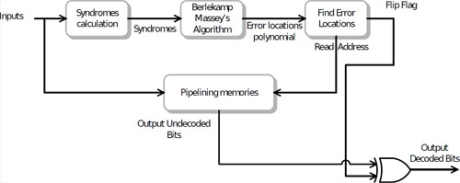

BCH Decoder

- BCH decoder compliant with the DVB-T2/S2 standard.

- Available for Altera/Xilinx FPGA or ASIC implementation.

- High speed design.

- BCH decoder works on GF(2M) where M = 16 or 14 and correctup to T errors where T = 10 or 12.

- Area and power optimized implementation.

-

oFEC Encoder and Decoder

- OpenROADM oFEC (Open Forward Error Correction) is a core element of the OpenROADM initiative, providing a standardized, open-source FEC solution for high-speed coherent optical networks.

- The oFEC IP cores deliver high coding gain through a fully parallel, pipelined decoder architecture with 3 soft-decision (SD) and 2 hard-decision (HD) decoding steps. It supports data rates from 200G to 800G, including Probabilistic Constellation Shaping (PCS) modes to enhance spectral efficiency, noise tolerance, and transmission reach.

-

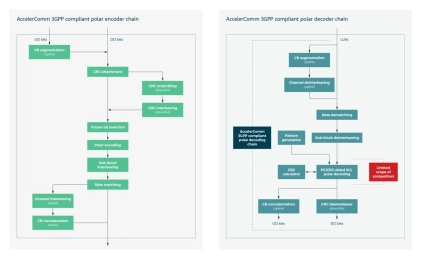

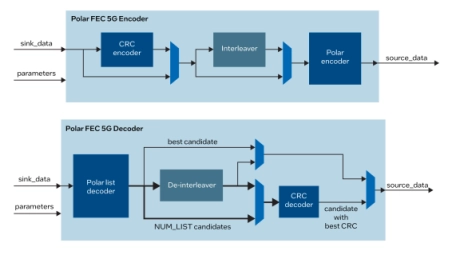

Polar Encoder / Decoder for 3GPP 5G NR

- The patented polar encoding and decoding IP for the 3GPP New Radio uplink and downlink includes the entire processing chain, to provide quick and easy integration and minimize the amount of extra work needed.

- The polar core uses PC- and CRC-aided SCL polar decoding techniques, in order to achieve compromise-free error correction performance.

-

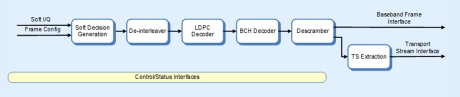

DVB-Satellite FEC Decoder

- The CMS0077 Satellite FEC Decoder has been designed specifically to meet the requirements of the DVB-S2 and DVB-S2X advanced wide-band digital satellite standards.

- The core provides all the necessary processing steps to convert a demodulated complex I/Q signal into a standard TS output stream.

-

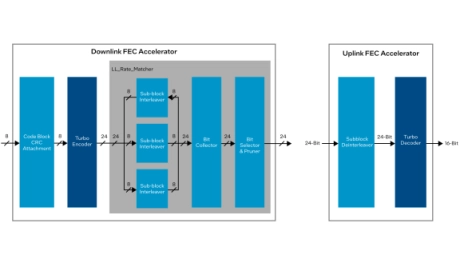

Turbo Intel® FPGA IP

- Forward-error correction (FEC) channel codes commonly improve the energy efficiency of wireless communication systems

- Turbo codes are suitable for 3G and 4G mobile communications and satellite communications

- You can use Turbo codes in other applications that require reliable information transfer over bandwidth- or latency-constrained communication links in the presence of data-corrupting noise. The 4G Turbo-V Intel® FPGA IP comprises a downlink and uplink accelerator for vRAN and includes the Turbo Intel® FPGA IP.

-

5G Polar Intel® FPGA IP

- The 5G Polar Intel® FPGA IP implements a forward error correction (FEC) encoder and decoder based on polar codes compliant with the 3rd Generation Partnership Project (3GPP) 5G specification for integration into your wireless design

- Polar codes represent an emerging class of error correction supporting the high throughput requirements for 5G new radio (NR).

-

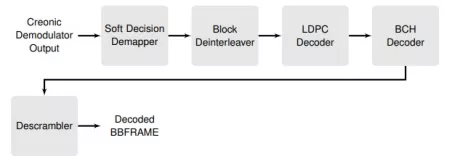

DVB-S2X Wideband BCH and LDPC Decoder

- Compliant with DVB-S2 and DVB-S2X

- Support for decoding of BBFRAMEs

- Support for ACM, CCM, and VCM

-

DOCSIS 3.1 LDPC Decoder (PLC / NCP / Data)

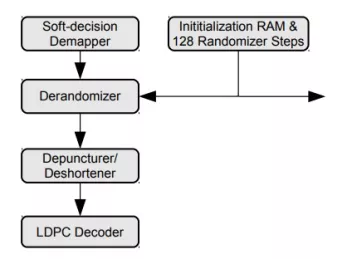

- Soft-Decision Demapper, Derandomizer, Deinterleaver, Depuncturer, and LDPC Decoder are included

- Support for 4k and 8K FFT sizes

- Support for 16-QAM modulation

-

Fast Fourier Transform IP Core

- Supports forward and inverse complex FFT

- Supports transform length (N) from 23 to 2¹⁶

- Supports scaled or unscaled IFFT output

- Implemented as pipelined streaming IO architecture

-

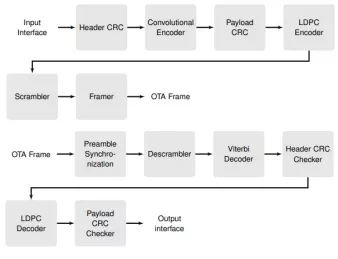

SDA OCT V3.0 Encoder and Decoder

- Compliant with "Optical Communications Terminal (OCT) Standard Version 3.0, Document ID: SDA-9100-0001-05, August 2021"

- Support for payload code rates 11/13, 22/29, 2/3, 1/2, and uncoded data