The Universal Serial Bus Debug Communication Link (USBDCL) provides an interface between an USB 2.0 bus and an AMBA-AHB bus.

An external PHY compliant with either UTMI, UTMI+ or ULPI is needed to connect to the USB.

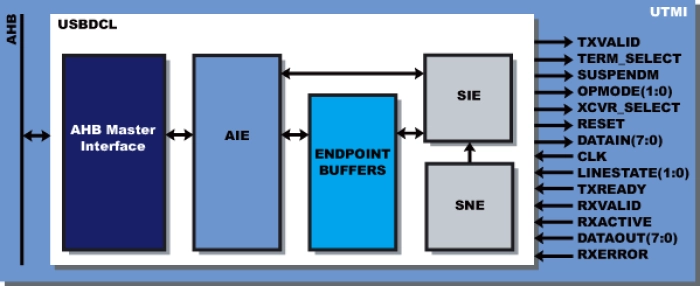

Architecture

The USBDCL is an AHB master and provides read and write access to the whole AHB address space using a simple protocol over two USB bulk endpoints. The USBDCL is a function implementation that utilizes the GRUSBDC device controller for the USB interface.

Protocol

The USBDCL protocol uses one IN and one OUT bulk endpoint (in addition to the mandatory control endpoint). Read and write commands to the AHB bus and write data are sent to the OUT endpoint. Read data is returned on the IN endpoint. The protocol is supported in the GRMON debug tool using libusb and provides maximum speeds of up to 30 MBit/s to the AHB bus over an USB 2.0 bus. The protocol specification is freely available so it is possible to develop own applications that utilize the USBDCL.