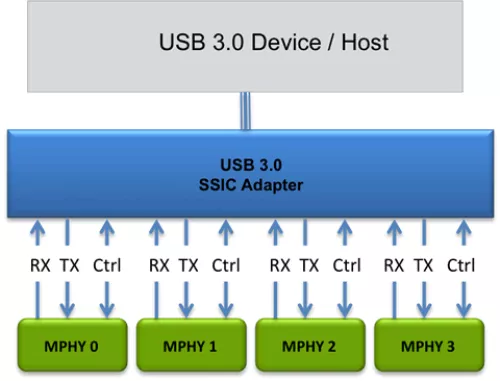

The Arasan Superspeed Inter-chip Controller (USB 3.0 SSIC Adapter) uses Arasan’s MIPI-M-PHY (Type-1) v. 3.0 to implement the SSIC adaptation to the USB3 PIPE interface. The Arasan USB 3.0 SSIC adapter is compliant with the “Inter-Chip supplement to the USB revision 3.0 specification, version 1.0” and the MIPI-M-PHY specification revision 3.0-r.03 and provides an effective data rate of up to 5.0 Gbps per lane, over 1 to 4 lanes of M-PHY. The USB 3.0 SSIC Bridge IP interfaces to the USB3 Device/Host controller with PIPE3 interface at 8/16/32-bit data width.

Leveraging the MIPI-M-PHY power management, SSIC adapter lowers the active power and idle power. The USB 3.0 SSIC adapter is optimized for power, area, and EMI robustness for embedded inter-chip interfaces.

The USB 3.0 SSIC Adapter is delivered as digital RTL.

USB 3.0 SSIC PHY

Overview

Key Features

- Compliant with SSIC specification 1.0

- Compliant with MIPI-MPHY (Type-1) specification Rev 3.0-r.03

- Interfaces to the USB3 Device/Host controller via the standard PIPE3 interface at 8/16/32-bit data widths

- Customizable to supports x1, x2, and x4 LANE configurations

- Uses standard RMMI interface @10/20/40-bits to interface with MPHY module

- MIPI-MPHY supports:

- HS-G1, HS-G2 and HS-G3 modes with data rate series A/B

- PWM-G1 for LS Mode

- Supports all the M-MPHY states as per SSIC specification (SLEEP, STALL, HIBERN8, HS-BURST, PWM-BURST) etc

- Provides access to M-TX and M-RX capabilities and attributes through memory mapped registers

- Operates with shared or non-shared reference clocks

Benefits

- Compliant with M-PHY and the relevant protocols standards

- Seamless interface to Arasan’s host and device controllers for those standards

- Configurable number of lanes

- Area and power efficient

Block Diagram

Deliverables

- RMM-compliant synthesizable RTL design in Verilog

- Easy-to-use test environment

- Synthesis scripts

- Technical documents

- Simulation scripts

Technical Specifications

Maturity

Pre-silicon

Availability

Now