NIST FIPS-197 Compliant High Throughput Rate AES IP Core

Overview

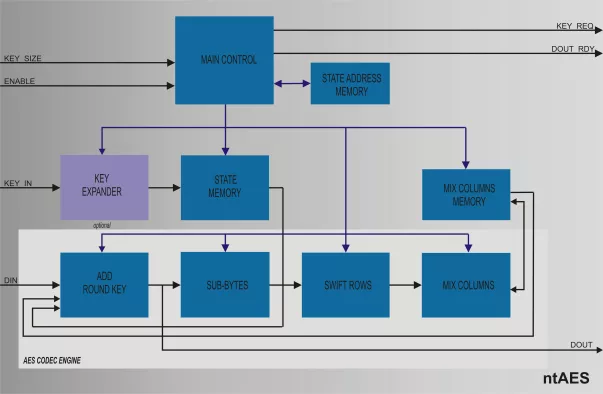

ntAES128 core implements the NIST FIPS-197 Advanced Encryption Standard and can be programmed to either encrypt or decrypt 128-bit blocks of data using a 128-bit, 192-bit or 256-bit key. The ntAES128 has been carefully designed for high throughput applications with optimal logic resources utilization. The encryptor core accepts a 128-bit plaintext input word, and generates a corresponding 128-bit ciphertext output word using a supplied 128, 192, or 256-bit AES key. The decryptor core provides the reverse function, generating plaintext from supplied ciphertext, using the same AES key as was used for encryption. The hardware roundkey expansion logic has been designed as a discrete building block. This allows either to build a complete stand-alone AES solution, or to save logic resources by leaving the key generation process to the user. Alternatively, the roundkey expansion logic can be shared between multiple encryption/decryption cores for optimal silicon area resources utilization. The implementation is very low on latency, high speed with a simple interface for easy integration in SoC applications.

Key Features

- Compliant to Advanced Encryption Standard (AES) (FIPS PUB 197)

- Supports both encryption and decryption functions

- Supports 128/192/256-bit Cipher keys

- 128-bit data block

- Supports ECB, CBC, CFB, OFB and CTR modes

- Optional Key Expansion module

- Supports I/O data flow control capability

- Exhibits highly optimized performance-silicon area ratio

- Ideal for high throughput rate applications

- Fully synchronous design

- Silicon proven in ASIC and FPGA technologies for a variety of applications

Block Diagram

Deliverables

- Fully commented synthesizable VHDL or Verilog source code or FPGA netlist

- VHDL or Verilog test benches and example configuration files

- C++ model

- Comprehensive technical documentation

- Technical support

Technical Specifications

Short description

NIST FIPS-197 Compliant High Throughput Rate AES IP Core

Vendor

Vendor Name

Foundry, Node

TSMC

Maturity

Silicon proven

Availability

Now