Image Stabilization IP Core

Overview

The S-COR-10 FPGA IP core for image stabilization in video stream images is designed for use in vision systems intended for various applications (security systems, specialized systems, etc.) that are based on FPGA. The core is a completed module suitable for use in FPGA projects. The core represents a simple data exchange interface that ensures easy integration into various systems. The core performs 2D (horizontal and vertical) image stabilization. The algorithms implemented in the core provide image stabilization with accuracy of 2 pixels. The core determines the offset of the image relative to the previous frame and adapted to the smooth movement of the field of view of the video source. The core doesn’t modify the input image, the core forwards horizontal and vertical offset values to other subsystems. Subsequently this information can be used to read image data from the corresponding addresses (with offset). Thus, the S-COR-10 IP core is a versatile module that allows its use in any FPGA projects for vision systems.

Key Features

- Max video frame size - 1024x1024 pixels.

- Min video frame size - 128x128 pixels.

- Offset determination accuracy - 2 pixels for a single offset

- Maximum offset of the current frame relatively to previous - 32 pixels in any direction

- Calculation time - No more than 3 ms. when for frame size 720x576 and no more than 10 ms. for frame size 1024x1024. The system frequency is 200 MHz.

- Input information requirements - In the images:

- no more than 20% of contrast moving objects,

- no less than 20% of contrast stationary background objects.

- Note: the data above is given for FPGA Kintex-7.

Benefits

- Intellectual Property object tracking cores (IP Cores) supplied by RIFTEK ensure stable tracking of various classes of objects such as vehicles, flying objects, surface objects and humans. The IP cores are capable of operation with any video sources featuring resolution up to 2048x2048 pixels. Video source for IP cores can be provided by both common cameras and thermal vision cameras. The IP cores allow simultaneous tracking of several objects and simultaneous detection of up to 128 moving objects. A simple data exchange interface ensures easy integration of the IP cores into any FPGA-base technical vision systems. The cores require a little use of FPGA resources, which allows one to combine several cores in one project. Our IP cores support all FPGA families of Xilinx company.

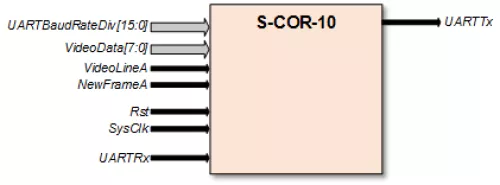

Block Diagram

Applications

- The core can be used in any vision applications such as security video surveillance systems and in special robotic vision systems.

Deliverables

- Synthesizable VHDL, full technical support

Technical Specifications

Short description

Image Stabilization IP Core

Vendor

Vendor Name

Maturity

Mature

Availability

Direct availability