NLM (Non Local Mean) is a noise reduction algorithm wherein the value of each pixel is determined a rectangle of pixels around that pixel (a “center patch”) with all identically-sized rectangles of pixels (“search patches”) within a relatively large rectangle around the pixel (the “search window”). A weight is then given to the center pixel of each “search patch” according to the distance of the corresponding search patch from the center patch, and the output pixel is derived by calculating the weighted average of all the pixels in the search window.

This algorithm is relatively complex, requiring a large number of gates. VLSI Plus V-NLM-01 product, however, significantly reduces the number of gates by performing two operations in each clock cycle, keeping an energy efficient architecture where consecutive operations are done on neighboring pixels.

Hardware NLM (Non-Local-Mean) Video Noise Reduction IP core

Overview

Key Features

- Efficient implementation of the NLM noise reduction algorithm

- Two clock per pixel

- Low power consumption

- Search window size and number of bits per pixel are parameters

Benefits

- state of the art video noise reduction algorithm, executed at real time

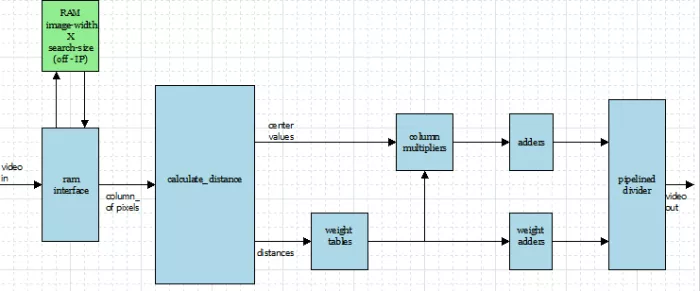

Block Diagram

Applications

- application processor

- video processors

- 3D imaging

Deliverables

- obfuscated Verilog RTL

- Bit-exact C model (executable only)

- Verilog Test Bench

Technical Specifications

Short description

Hardware NLM (Non-Local-Mean) Video Noise Reduction IP core

Vendor

Vendor Name

Maturity

new product

Availability

now

Related IPs

- 2D GPU Hardware IP Core

- Cryptographically Secure Pseudo Random number Generator IP Core

- RTP/UDP/IP Protocol Hardware Stack – Raw, Uncompressed RGB/YUV Video Streams Packet Processing

- Multi-Channel Flex DMA IP Core for PCI Express

- High Channel Count DMA IP Core for PCI-Express

- 3D OpenGL ES 1.1 GPU IP core