Highly versatile, high performance advanced Ethernet Switch with an extensive set of QoS features and statistics.

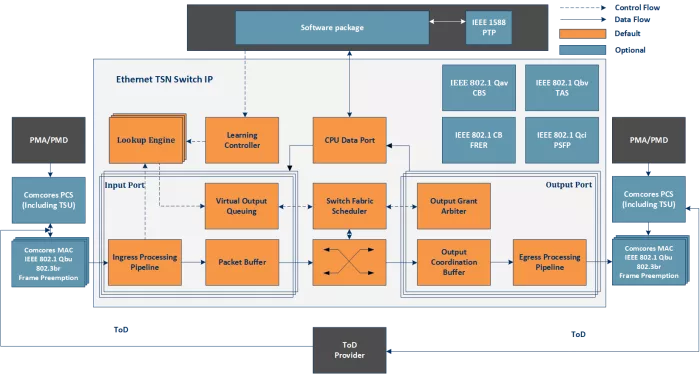

The 10M/100M/1G/10G/25G Ethernet Switching IP is an advanced Ethernet TSN Switch IP with an extensive set of QoS features and statistics. The Comcores Ethernet TSN Switch IP supports up to 8 queues, classification, VLAN 802.1Q, multicast and broadcast as well as IEEE 1588 transparent clock. Each port provides a native interface for Ethernet PHY devices. IEEE 802.1 Protocol Implementation Conformance Statement is available, specifying exact feature-set.

The Ethernet TSN Switch IP provides support for key TSN features including IEEE 802.1Qbu and 802.3br Frame preemption, 802.1Qbv Time aware shaping, 802.1Qav Credit based shaping, 802.1Qci Per-Stream Filtering and Policing, and 802.1CB Frame replication and elimination for reliability. This enables the use of the IP in high speed time-critical applications.