AES-CTR, Advanced Encryption Standard (256-bit key), Counter Mode IP Core

The AES-CTR IP cores implement the AES in Counter mode, effectively turning a block cipher into a stream cipher while providing m…

Overview

The AES-CTR IP cores implement the AES in Counter mode, effectively turning a block cipher into a stream cipher while providing multiple implementation advantages.

Advanced Encryption Standard (AES) is the predominant block cipher technique for symmetric encryption, serving as the primary encryption algorithm for protecting data communication and storage. Xiphera’s Symmetric Encryption portfolio offers a wide range of IP cores for AES algorithms optimised for optimal resource usage and performance.

Xiphera’s AES-CTR IP cores implement the AES in Counter mode, a method that effectively turns a block cipher into a stream cipher while providing multiple advantages from an implementation perspective.

Xiphera’s high-speed AES-CTR (XIP1103H) is designed for seamless integration within FPGA- and ASIC-based designs, following a vendor-agnostic approach where the IP core functionalities are independent of any manufacturer-specific features. The IP core is validated under the CAVP validation program from the U.S. NIST (National Institute of Standards and Technology).

Key features

- Moderate resource requirements: The high-speed AES-CTR does not require any multipliers or DSPBlocks in a typical FPGA implementation.

- Performance: Despite its moderate size, the IP core achieves a throughput in the tens of Gbps range.

- Standard Compliance: Xiphera’s AES-CTR is fully compliant with both the Advanced Encryption Algorithm standard, as well as with the Counter Mode standard.

- CAVP validation: The AES-CTR IP core from Xiphera has received the CAVP validation from the U.S. National Institute of Standards and Technology (NIST).

- 128-bit and 256-bit Interfaces ease the integration of the high-speed AES-CTR with other FPGA logic and/or control software.

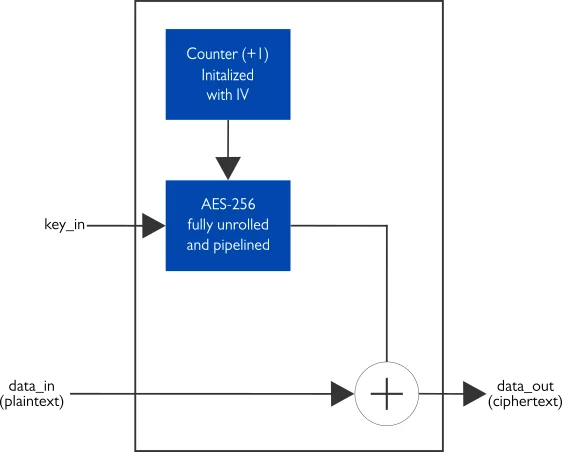

Block Diagram

Benefits

- Fully digital design

- Portable to any ASIC or FPGA technology

- Fully standard compliant

- Easy to integrate

- Several bus interfaces available

- IP core designed in-house at Xiphera

- Technical support by the original designers and cryptographic experts

- CAVP validated

Applications

- XIP1103H protects the confidentiality of the encrypted plaintext, and to additionally provide authenticity protection XIP1103H can be used as a building block in AES-GCM (Galois Counter Mode) (for example, Xiphera’s IP cores XIP1113B and XIP1113H have XIP1103H for confidentiality protection).

- An alternative way to protect both confidentiality and authenticity is to use XIP1103H in combination with a keyed message authentication code (such as Xiphera’s KMAC IP core).

What’s Included?

- XIP1103H can be shipped in a number of formats, including netlist, source code, or encrypted source code.

- Additionally, synthesis scripts, a comprehensive testbench, and a detailed datasheet including an integration guide are included.

Specifications

Identity

Security

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Symmetric Crypto IP core

CXL - The Latest Specification in Secured Network Traffic

Securing your apps with Public Key Cryptography & Digital Signature

RoT: The Foundation of Security

Tailoring Root Of Trust Security Capabilities To Specific Customer Needs

Symmetric Cryptographic Offload Options for SoC Designers

Frequently asked questions about Symmetric Cryptography IP cores

What is AES-CTR, Advanced Encryption Standard (256-bit key), Counter Mode IP Core?

AES-CTR, Advanced Encryption Standard (256-bit key), Counter Mode IP Core is a Symmetric Crypto IP core from Xiphera Ltd listed on Semi IP Hub.

How should engineers evaluate this Symmetric Crypto?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Symmetric Crypto IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.