AES-GCM, Advanced Encryption Standard (256-bit key), Galois Counter Mode IP Core

XIP1113B from Xiphera is a balanced Intellectual Property (IP) core implementing the Encryption Standard (AES) in Galois Counter …

Overview

XIP1113B from Xiphera is a balanced Intellectual Property (IP) core implementing the Advanced Encryption Standard (AES) in Galois Counter Mode (GCM). AES-GCM is a widely used cryptographic algorithm for Authenticated Enryption with Associated Data (AEAD) purposes, as it provides both data confidentiality and authenticity.

XIP1113B has been designed for easy integration with FPGA- and ASIC-based designs in a vendor-agnostic design methodology, and the functionality of XIP1113B does not rely on any FPGA manufacturer-specific features.

The main functionality of XIP1113B depends on the mode of operation. When XIP1113B operates in the encryption and authentication tag calculation mode, it encrypts the incoming plaintext blocks into ciphertext blocks, and in addition to this also calculates a 128 bits long authentication tag from both the incoming plaintext and associated data. When XIP1113B operates in the decryption and tag validity cheching mode, it decrypts the incoming ciphertext blocks into plaintext blocks, and validates the received authentication tag value by calculating the tag from the incoming ciphertext and associated data blocks and comparing the resulting tag value with the received tag value. As defined by the GCM mode of operation, associated data is included in the authentication tag calculation.

XIP1113B can also operate with zero-length associated data, meaning that XIP1113B treats all sig nals on the input data_in as plaintext to be encrypted or as ciphertext to be decrypted. XIP1113B can also operate with zero-length plaintext or ciphertext, in which case it acts only as an authen ticator or authentication validity checker.

XIP1113B outputs first the associated data, followed by encrypted plaintext or decrypted cipher text (depending on the mode of operation), and as the last output the tag value and associated status signals.

Key features

- Compact resource requirements: The entire XIP1113B requires 3571 Adaptive Lookup Mod ules (ALMs) (Intel® Agilex® I), and does not require any multipliers, DSPBlocks or internal memory1 in a typical FPGA implementation.

Performance: Despite its compact size, XIP1113B achieves a throughput in the Gbps range2, for example 4.44+ Gbps in AMD® Kintex® UltraScale+.

Standard Compliance: XIP1113B is fully compliant with both the Advanced Encryption Algo rithm (AES) standard [2], as well as with the Galois Counter Mode (GCM) standard [3].

Test Vector Compliance: XIP1113B passes all test vectors specified in [1].

Flexible Interfaces ease the integration of XIP1113B with other FPGA logic and/or control software.

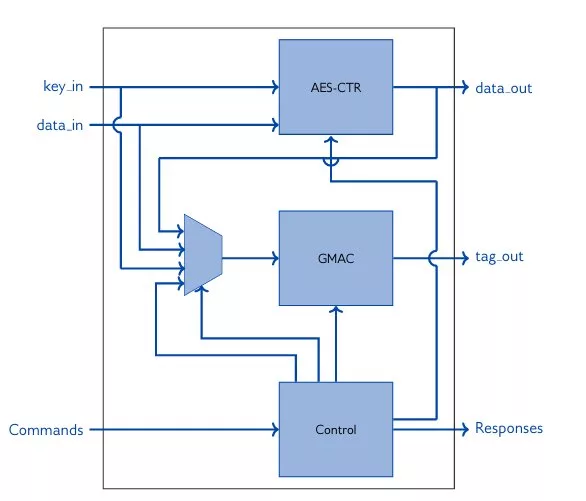

Block Diagram

Benefits

- Fully digital design

- Portable to any ASIC or FPGA technology

- Fully standard compliant

- Easy to integrate

- Several bus interfaces available

- IP core designed in-house at Xiphera

- Technical support by the original designers and cryptographic experts

- CAVP validated

Applications

- XIP1113B has several applications, as AES-GCM is a popular AEAD algorithm in a number of standardized communications protocols, including IPSEC, MACSEC and TLS (Transport LayerSecurity) versions 1.2 and 1.3. Additionally, AES-GCM is used in fibre channel communications and tape storage applications.

What’s Included?

- XIP1113B can be shipped in a number of formats, including netlist, source code, or encrypted source code.

- Additionally, synthesis scripts, a comprehensive testbench, and a detailed datasheet including an integration guide are included.

Specifications

Identity

Security

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Symmetric Crypto IP core

CXL - The Latest Specification in Secured Network Traffic

Securing your apps with Public Key Cryptography & Digital Signature

RoT: The Foundation of Security

Tailoring Root Of Trust Security Capabilities To Specific Customer Needs

Symmetric Cryptographic Offload Options for SoC Designers

Frequently asked questions about Symmetric Cryptography IP cores

What is AES-GCM, Advanced Encryption Standard (256-bit key), Galois Counter Mode IP Core?

AES-GCM, Advanced Encryption Standard (256-bit key), Galois Counter Mode IP Core is a Symmetric Crypto IP core from Xiphera Ltd listed on Semi IP Hub.

How should engineers evaluate this Symmetric Crypto?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Symmetric Crypto IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.