055TSMC_CML_01 is a library including:

- CML receiver (CML_RX);

- CML transmitter (CML_TX).

The CML_RX block is intended to receive a CML signal and convert it to a CMOS signal. The CML_TX block is intended to convert signal from CMOS to CML standard and transmit CML signal to external circuits. CML_TX has pre-emphasis circuit.

IP technology: TSMC 55nm CMOS EF technology.

IP status: pre-silicon verification.

Total area:

- CML_RX – 121×121 um2;

- CML_TX – 110×171 um2.

4 Gbps DDR CML receiver and transmitter

Overview

Key Features

- TSMC CMOS 55 nm

- TIA/EIA-644 LVDS standards

- Data rate (receive/transmit): up to 4 Gbps (DDR mode)

- 1.2V digital voltage supply

- 1.2V core voltage supply

- 1.2V CMOS input/output logic control signals

- Temperature range: -40 °C to + 85 °C

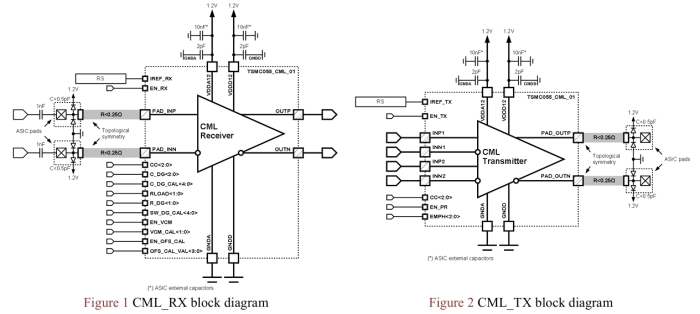

Block Diagram

Applications

- Point-to-point data transmission

- Multidrop buses

- Clock distribution

- Backplane receiver

- Backplane data transmission

- Cable data transmission

Deliverables

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Technical Specifications

Short description

4 Gbps DDR CML receiver and transmitter

Vendor

Vendor Name

Foundry, Node

TSMC CMOS 55 nm

Maturity

pre-silicon verification

Availability

Now

TSMC

Pre-Silicon:

55nm

FL