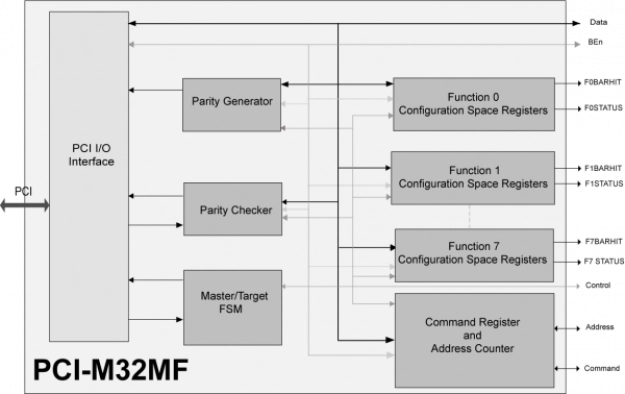

The PCI-M32MF implements a master/target PCI interface compliant with the PCI 2.3 specification. It supports a 32-bit address/data bus and operates up to 33 MHz PCI clock.

The core offers one to eight independent PCI functions in a single chip, each implementing 64 to 256 bytes of PCI Configuration Space registers as required. Each function supports up to six Base Address Registers, with both I/O and Memory space decoding from 16 bytes up to 4GB.

The PCI-M32MF builds on more than 15 years of CAST PCI IP expertise and has been designed for straightforward reuse, with proven design practices that ensure easy integration and smooth technology mapping. The core is available in synthesizable RTL or as a targeted FPGA netlist, and is delivered with everything required for rapid and successful integration and implementation.