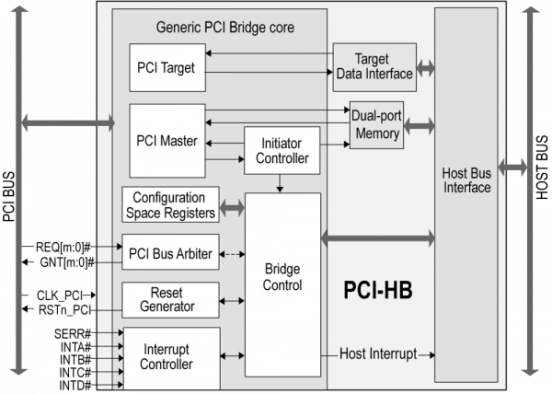

This PCI Host Bridge IP core enables data transfers between a host processor and PCI bus based devices.

The bridge allows the host to initiate PCI accesses or to respond to transactions initiated by other PCI devices.

The core complies with the PCI bus specification versions 3.0 and 2.3, and can act as a PCI master and target. Furthermore, it implements PCI bus arbitration, supporting up to seven PCI bus agents, PCI reset signal generation, and all types of PCI transactions provisioned by the standard.

The PCI-HB builds on more than 15 years of CAST PCI IP expertise and has been designed for straightforward reuse, with proven design practices that ensure easy integration and smooth technology mapping. The core is available in synthesizable RTL or as a targeted FPGA netlist, and is delivered with everything required for rapid and successful integration and implementation.