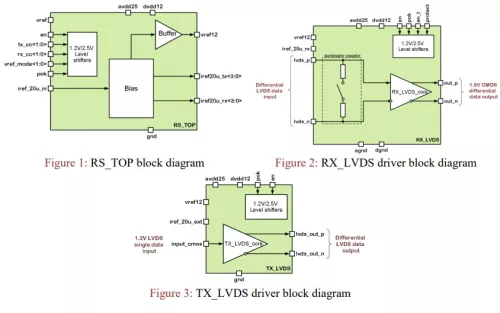

055TSMC_LVDS_03 is a library including:

- Transmitter LVDS driver (TX_LVDS);

- Receiver LVDS driver (RX_LVDS);

- Reference current/voltage generators (RS_TOP).

The RS_TOP block is intended to output reference currents and voltage for RX_LVDS driver and TX_LVDS driver.

Composing of LVDS library components allows to design a device with up to 2 pairs of data channels and 2 pairs of synchronization channels.