The OT3124bt is a flexible clock multiplier PLL function with a wide range of input and output frequencies. High range M divider allows this PLL to be driven by low power non-overtone crystal oscillator circuits if required. This IP is designed for the TSMC 0.18u digital or mixed signal family of CMOS processes.

1.2GHz General Purpose PLL for TSMC 0.18u Processes

Overview

Key Features

- Wide range N, M integer dividers.

- 600MHz – 1.2GHz output frequency range.

- Comparable frequency range 20MHz – 200MHz.

- 18pS RMS cycle to cycle jitter at 1.2GHz.

- Lock-detect function.

- Bypass function.

- Well defined startup behavior.

- -40°C to 140°C temperature operation.

- Available divider selection program.

- Small cell area: 0.06mm2 in 0.18µ CMOS.

- 8mW typical power dissipation.

- 1.8V digital and analog supplies.

- 0.18µ CMOS process compatibility.

- Silicon proven architecture.

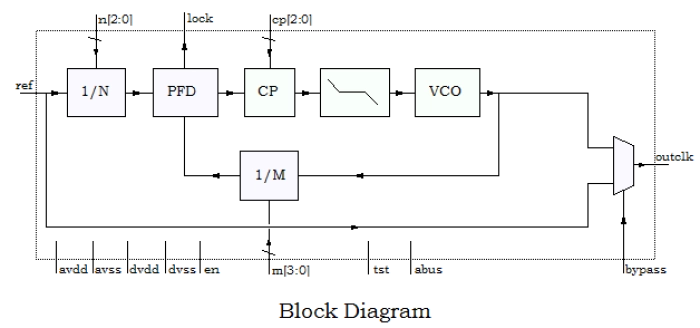

Block Diagram

Technical Specifications

Short description

1.2GHz General Purpose PLL for TSMC 0.18u Processes

Vendor

Vendor Name