UCIe Controller add-on CXL3 Protocol Layer

The UCIe Controller IP encompasses the Die-to-Die Adapter Layer and Protocol Layer for widely used protocols, such as PCI Express…

Overview

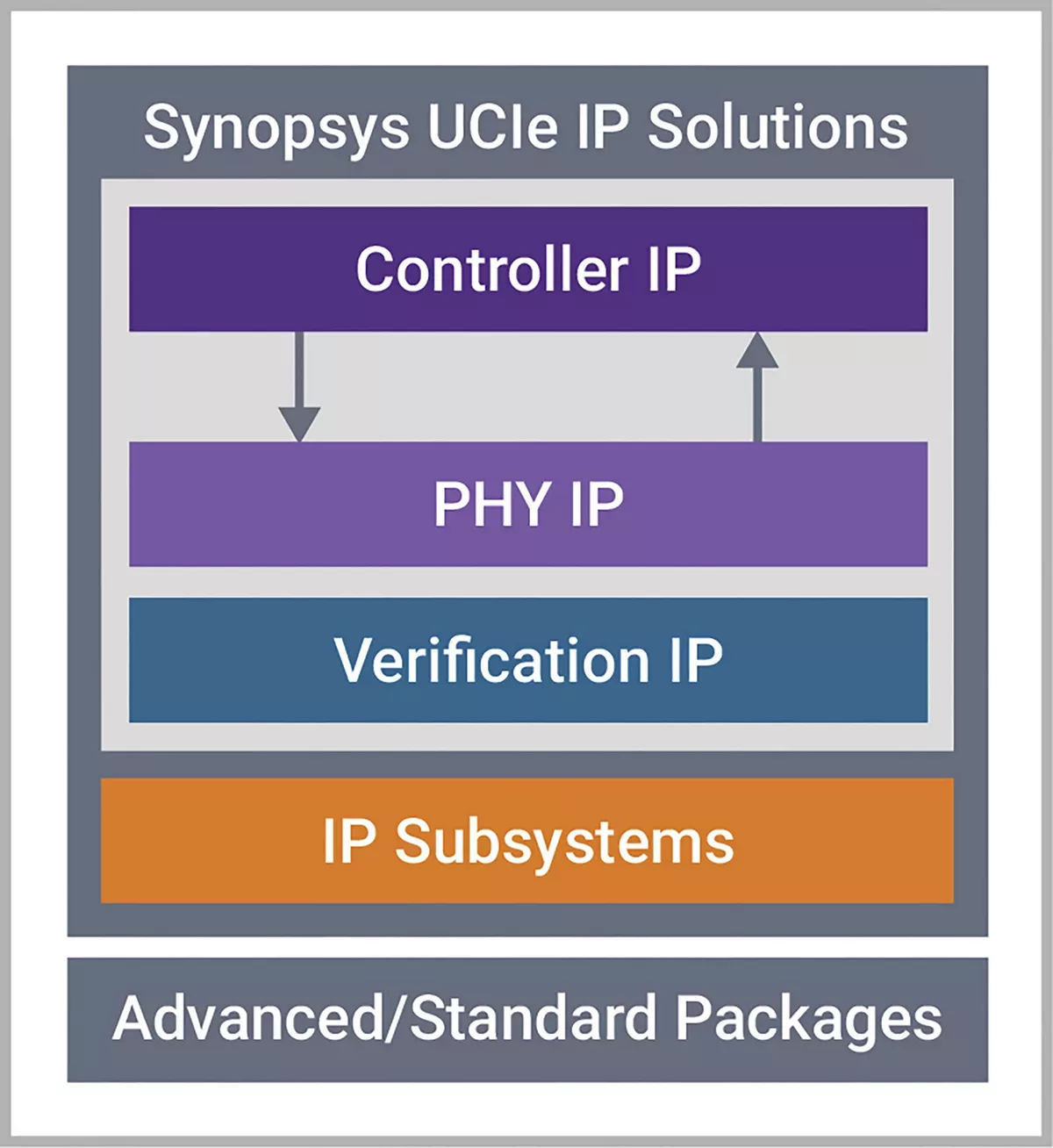

The UCIe Controller IP encompasses the Die-to-Die Adapter Layer and Protocol Layer for widely used protocols, such as PCI Express and CXL. The IP enables latency-optimized NoC-to-NoC links with AXI, CXS, CHI C2C, and streaming protocols. The controller IP implements an RDI interface to the PHY and an FDI interface between the Die-to-Die Adapter and Protocol Layers. These interfaces include all the necessary sideband signaling for protocol discovery and negotiation between two dies, and smooth link initialization and operation. The UCIe Controller IP offers maximum performance, minimum latency, and implementation flexibility. The IP ensures link reliability by supporting retry mechanism and performing CRC or parity checks for error detection. The flexible IP implementation targets single-module or multimodule configurations, both for advanced and standard packages. The UCIe Controller IP along with the UCIe PHY IP and Verification IP deliver a complete solution for die-to-die connectivity in multi-die designs. The UCIe Controller IP along with the UCIe PHY IP and Verification IP deliver a complete solution for die-to-die connectivity in multi-die designs.

Key features

- Low latency controller for UCIe-based multi-die designs

- Includes Die-to-Die Adapter layer and Protocol layer

- Supports on-chip interconnect fabrics including AXI, CHI C2C, CXS, PCIe, CXL, and streaming

- Error detection and correction with optional CRC and retry functionality

- Supports single-module and multi-module UCIe configurations

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about UCIe IP core

Cadence Tapes Out 32GT/s UCIe IP Subsystem on Samsung 4nm Technology

UCIe D2D Adapter Explained: Architecture, Flit Mapping, Reliability, and Protocol Multiplexing

The Next-Generation UCIe IP Subsystem for Advanced Package Designs

Cadence Silicon Success of UCIe IP on Samsung Foundry’s 5nm Automotive Process

40G UCIe IP Advantages for AI Applications

Frequently asked questions about UCIe IP cores

What is UCIe Controller add-on CXL3 Protocol Layer?

UCIe Controller add-on CXL3 Protocol Layer is a UCIe IP core from Synopsys, Inc. listed on Semi IP Hub.

How should engineers evaluate this UCIe?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UCIe IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.