Increasing bandwidth to 128 GB/s with a tailored PCIe 6.0 IP Controller

By Romain Tourneau, PLDA

While the PCIe 6.0 specification is expected to be finalized and released later in 2021, PLDA has been hard at work to address the needs of early adopters looking for the most advanced PCIe 6.0 IP solution for their SoCs and ASICs.

Although PCIe 5.0-enabled systems are not yet available in the general market, Automotive, AI and IoT system designers are already pushing for more bandwidth than 5.0 supports. Self-driving cars are the perfect example of this need -- to continuously sense and react to the surrounding environment in real time, the autonomous driving systems need to access historical data stores containing weather, obstacles, and traffic and road conditions. These enormous data dumps, accounting for every minute, hour, day and year that a driverless car is out on the road, have to be managed and stored. Of course, a large part of a driverless car's environment will be accounting for other vehicles. Thus, driverless cars must be equipped with a myriad of sensors creating and transferring machine-to-machine data with speeds of up to 1GB per second. Big data storage will then be an absolute necessity, along with smart management of the data feed, its sensors, and vehicle libraries. Within this example, PCIe 6.0 is the best protocol candidate to interconnect the different elements.

At PLDA, we develop leading edge high-speed interfaces, with a strong development focus on PCIe. While PCIe is found in many applications, and can be delivered “off the shelf”, PCIe can become “strategic” and highly sensitive in high-end use cases. With the latest PCIe specifications, a growing number of features associated with an exponential quantity of verification tests mean that IP development has become more and more complex. This level of complexity requires a dedicated team working together, focused on delivering high quality, high performance, reliable IP.

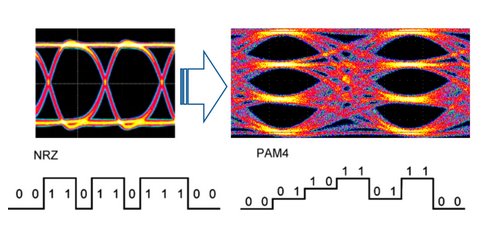

To achieve the performance of 128GB/s on a x16 link, PCIe 6.0 has broken some of its previous rules. On the electrical layer, it now uses a PAM4 modulation (“Pulse Amplitude Modulation with four levels”) that enables it to run 2 bits/cycle instead of 1 bit/cycle with the previous NRZ modulation (Figure 1). While this means PCIe 6.0 can effectively double its bandwidth vs 5.0, it also generates a higher Bit Error Rate (BER). To compensate for high BER, the specification implements a new feature called Forward Error Correction (FEC), which enables it to avoid packet replay for every bit-error. It works in conjunction with strong CRC (Cyclic Redundancy Check) to keep Link Retry probability under 5x10-6. This new FEC feature targets an added latency under 2ns.

The PCIe 6.0 Specification also introduces L0p, enabling traffic to be transmitted on a reduced set of lanes, which means other lanes can be turned off, thus reducing power consumption without impacting traffic flow.

Fig 1: Comparison between NRZ modulation and PAM4 modulation

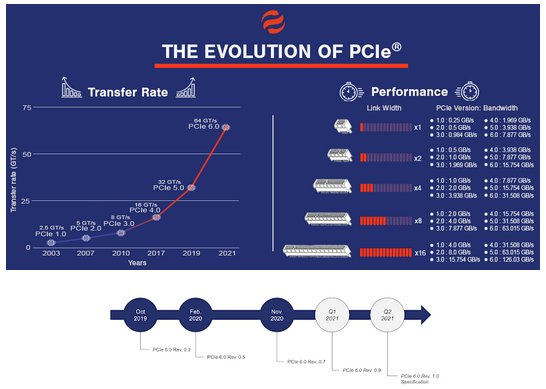

We are still some time away from the release of version 0.9 of the PCIe 6.0 specification. For those not familiar with the release process, version 0.9 is usually the close-to final version, meaning there should not be any major new features or modifications beyond the version 0.9 PCIe 6.0 architecture. We expect version 1.0 of the specification to be publicly released in the second quarter of this year. (Figure 2)

Fig 2: Estimated PCI-SIG roadmap for PCIe 6.0 specification

As the PCIe 6.0 specification advances towards finalization, PLDA is designing its XpressRICH for PCIe 6.0 controller IP. Today, we are pleased to announce that this IP will support the following features:

- Backwards compatibility to PCIe 1.1

- Fully parameterized

- Native Tx/Rx or TLP user interface

- PIPE LPC and SerDes mode

- Same RTL for ASIC and FPGA implementation

Furthermore, PLDA has developed a complete ecosystem of complementary partners who are involved in this mission of delivering the most optimized IP solution, tuned to customers’ needs. Currently, we are working with high-end PHY IP providers to co-design a diversified list of pre-integrated PHY and Controller solutions in order to achieve best-in class solutions for PCIe 6.0. In addition, we are building a strong ecosystem of Verification IP and tools to further strengthen the ecosystem.

If you see a need for PCIe 6.0 in your systems, this is the perfect time to contact us to align roadmaps and discuss requirements.

Related Semiconductor IP

- PCIe 6.0 PHY, SS SF2A x4 1.2V, N/S for Automotive, ASIL B Random, AEC-Q100 Grade 2

- PCIe 6.0 PHY G2 , SS SF4X x4, North/South (vertical) poly orientation

- PCIe 6.0 PHY, TSMC N3A x4 1.2V, North/South (vertical) poly orientation for Automotive, ASIL B Random, AEC-Q100 Grade 2

- PCIe 6.0 Integrity and Data Encryption Security Module

- PCIe 6.0 / CXL 3.0 PHY & Controller

Related Articles

- How to accelerate memory bandwidth by 50% with ZeroPoint technology

- Leveraging IBIS-AMI Models to Optimize PCIe 6.0 Designs

- A comprehensive approach to enhancing IoT Security with Artificial Intelligence

- PCIe IP With Enhanced Security For The Automotive Market

Latest Articles

- Assertain: Automated Security Assertion Generation Using Large Language Models

- VolTune: A Fine-Grained Runtime Voltage Control Architecture for FPGA Systems

- A Lightweight High-Throughput Collective-Capable NoC for Large-Scale ML Accelerators

- Quantifying Uncertainty in FMEDA Safety Metrics: An Error Propagation Approach for Enhanced ASIC Verification

- SoK: From Silicon to Netlist and Beyond Two Decades of Hardware Reverse Engineering Research