Seven Key Advantages of Implementing eFPGA with Soft IP vs. Hard IP

eFPGA (embedded FPGA) technology currently has limited suppliers in the market. Menta stands out as the only provider offering fully flexible IP (intellectual property) based entirely on standard cells. This architectural approach enables Menta’s eFPGA IP to be implemented across any technology node and precisely tailored to specific performance and power specifications. The company’s advanced technology delivers remarkable adaptability, allowing for integration for critical applications across medical, automotive and industrial domains, including the particularly challenging environments encountered in space.

Let’s explore what true soft IP means and why you will undoubtedly prefer a soft IP solution over a hard IP, given its compelling advantages and superior flexibility across various implementation scenarios.

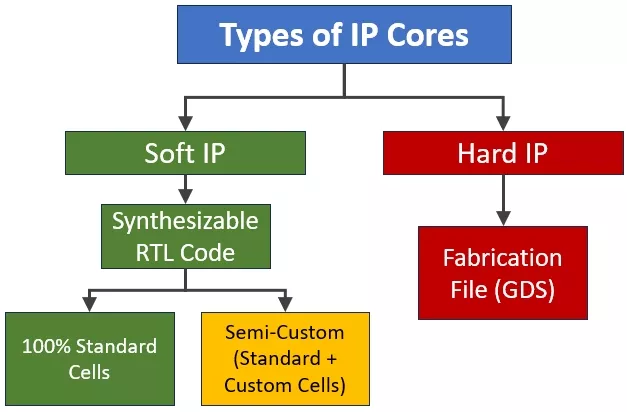

First, let’s clearly distinguish between soft IP and hard IP in the ASIC domain. Hard IP is delivered as a binary database (GDSII) containing the complete mask layout. This represents a finished product specifically designed for a particular foundry, process node, metal stack and process options, ready for direct physical placement into an ASIC. In contrast, soft IP is typically described using RTL languages such as Verilog, System Verilog or VHDL. The key advantage of soft IP is its flexibility—it can be synthesized to work with various foundries, process nodes, metal stacks and process options, rather than being locked to a single manufacturing specification.

For soft IP, an important distinction must be made. While some suppliers market their solutions as soft IP, these often contain blocks of custom hard IP, more accurately described as semi-custom. True soft IP consists exclusively of standard cells – fundamental electronic components like buffers, NAND gates and flip-flops that come with comprehensive layout specifications, timing characteristics and power consumption data. These logic cells undergo rigorous characterization by semiconductor foundries or standard cell providers and are verified using industry-standard EDA tools during synthesis and place-and-route processes. The cells are extensively evaluated for power consumption, performance capabilities and physical area requirements (PPA) across various conditions including process variations, temperature fluctuations and voltage changes. They also undergo thorough reliability, aging or even radiation testing for rad-hard products. For the most critical standard cells, foundries implement continuous production monitoring using specialized test structures to maintain quality.

Embedded FPGA IP providers can be classified as either hard IP, semi-custom IP or 100% soft IP. Menta is the only 100% soft IP provider with patented solutions that optimize and make this highly efficient, resulting in the following key advantages for companies implementing our technology.

1- Foundry Availability

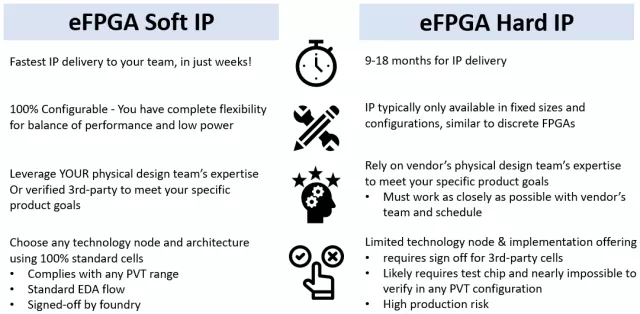

Soft IP eFPGAs offer unmatched flexibility, functioning seamlessly with any foundry, process, metal stack, standard cells and process options. They directly leverage the foundry’s extensive experience with standard cells, guaranteeing superior reliability, aging characteristics and qualifications. This approach delivers optimal yield results since the performance metrics are thoroughly documented, characterized and can be precisely calculated by the foundry itself—eliminating any need to depend on potentially biased eFPGA IP vendor claims. With soft IP, your design preferences remain paramount, as you’re never forced toward specific metal stack configurations or process options. While hard IP providers may advertise readily available off-the-shelf solutions, these are invariably locked into highly specific configurations designed for previous customers’ requirements, limiting your design freedom.

2- Specialized Cells Option

Soft eFPGA IP delivers a compelling advantage by enabling the use of specialized standard cells, including cells specifically characterized for automotive, aerospace and industrial applications. This versatility clearly addresses the unique requirements of these demanding markets, ensuring optimal performance in specialized environments.

3- Foundry Sign-Off

Soft eFPGA IPs seamlessly integrate with industry-standard sign-off flows and quality assurance processes from leading foundry and EDA vendors. This gives you complete control over PPA optimizations across any process, voltage and temperature range. The comprehensive verification ecosystem enables thorough validation through gate-level simulation, formal verification and even emulation—all without dependency on proprietary eFPGA vendor models, ensuring both reliability and design freedom.

4- Customer Control

Harness the full value of your team’s physical design expertise for the most optimal implementation. Additionally, leverage Menta’s physical design specialists’ knowledge or partner with your preferred design firm to maximize efficiency and quality in your projects.

5- Highly Customizable

Soft eFPGA IP architecture provides precisely tailored customization to your exact requirements, delivering measurably improved power, performance and area metrics. This granular adaptability creates a clear competitive advantage in the marketplace. Since eFPGA IPs can occupy significant portions of your ASIC/SoC design, optimizing their layout is essential for maximizing top-level routing efficiency. The strategic decision between square or rectangular configurations, combined with thoughtful pin placement, demonstrably enhances integration success and minimizes routing congestion in your final design—resulting in easier integration and faster time to market.

6- Rapid Delivery

Soft eFPGA IP can be delivered in less than two weeks, providing a clear advantage for accelerating project timelines. This solution offers exceptional flexibility by accommodating last-minute design modifications, enabling you to implement critical changes even during the final development stages. When engineering changes are needed, soft eFPGA IP ensures rapid turnaround times—a stark contrast to hard IP solutions, which typically reset the entire design cycle and cause substantial delays of several months. This time-saving capability translates directly to faster market entry and competitive advantage.

7- 100% Unique IP

Each Menta eFPGA IP is specifically tailored to individual customer implementations and securely tracked using a unique blockchain ID and certificate. This approach not only ensures complete isolation between implementations but also provides superior security by generating a distinct bitstream for every IP instance, making it virtually impossible for unauthorized parties to reverse-engineer or compromise the FPGA design.

What is Menta offering?

Menta delivers a superior soft eFPGA IP solution with all the compelling advantages mentioned above. Its innovative DFF based architecture enables standard DfT (design for test) implementation with nearly 100% coverage and reduces bitstream size by up to 4x compared to competitors, resulting in significant cost savings for embedded or on-board non-volatile memory. With Menta’s highly customizable eFPGA IPs, customers can precisely tailor their solution by adjusting not only the number of LUTs but also the quantity and type of DSPs, embedded RAM and even routing channels for higher LUT density packing. For maximum performance optimization, you can seamlessly integrate your own hard macros to enhance PPAs for specific applications. The powerful Menta Origami Programmer software adapts effortlessly to your needs, while semi-architectural licensing options provide clear cost control across multiple devices.

What about physical implementation of Menta soft eFPGA IP?

Physical implementation of a Menta soft eFPGA IP is remarkably straightforward and efficient. Menta has developed a robust eFPGA IP along with comprehensive methodology and scripts that guarantee seamless integration within your existing EDA flow – particularly excelling in critical areas such as timing constraints and timing loops management. With nearly two decades of specialized experience in eFPGA IP development, Menta’s dedicated ASIC team stands ready to provide expert support throughout your implementation journey. The physical implementation process typically completes in just 1 to 5 months, ensuring minimal impact on your overall project timeline.

While we have spoken about the clear advantages of soft IP, some customers lack the physical design resources to implement this IP. In these cases, Menta offers its eFPGA IP as a hard IP by handling the complete physical implementation process on your behalf. Alternatively, you can collaborate with one of our trusted partner design houses (including IC’Alps, Presto Engineering, SemiFive, Trusted Semiconductor Solutions – visit our website for the most current partner list) or work with your own preferred design partner.

The proven reliability of Menta v5 eFPGA IP is demonstrated through successful tape-outs across 6 different foundries, spanning 12 distinct process nodes from established legacy technologies to cutting-edge advanced nodes.

Seeking flexibility and adaptability? Menta’s eFPGA IP solution can be 100% customized to your exact needs, saving you time and money while helping you differentiate your products and get them to market quickly. Break free from rigid IP constraints of hard IP and let Menta’s tailored approach empower your innovation.

About Menta

Menta, a privately held company, provides 100% third-party standard-cell embedded FPGA intellectual property (IP) for system-on-chip (SoC), application-specific integrated circuit (ASIC) and application-specific standard product (ASSP) designs. Our innovative technology allows users to easily update silicon post-production, whether to fix a bug, implement customer-specific features, adapt to evolving standards or enhance security. Menta’s IPs are delivered with the Origami toolchain, which generates the bitstream directly from register transfer level (RTL), including synthesis.

Contact us at: info@menta-efpga.com

Related Semiconductor IP

- eFPGA Soft IP

- eFPGA on GlobalFoundries GF12LP

- eFPGA IP — Flexible Reconfigurable Logic Acceleration Core

- Heterogeneous eFPGA architecture with LUTs, DSPs, and BRAMs on GlobalFoundries GF12LP

- Radiation-Hardened eFPGA

Related Articles

- The Hard Facts about Soft Interconnect IP

- eFPGA IP Density, Portability & Scalability

- CPU Soft IP for FPGAs Delivers HDL Optimization and Supply Chain Integrity

- Menta eFPGA IP for Edge AI

Latest Articles

- AutoGNN: End-to-End Hardware-Driven Graph Preprocessing for Enhanced GNN Performance

- LUTstructions: Self-loading FPGA-based Reconfigurable Instructions

- CQ-CiM: Hardware-Aware Embedding Shaping for Robust CiM-Based Retrieval

- GenAI for Systems: Recurring Challenges and Design Principles from Software to Silicon

- Creating a Frequency Plan for a System using a PLL