TSN Ethernet Subsystem Available from CAST Proven at IIC and LNI Plugfests

WOODCLIFF LAKE, NJ, USA -- September 05 2018 -- A Time Sensitive Networking (TSN) subsystem for Automotive and Industrial Ethernet designed by Fraunhofer IPMS and available from semiconductor intellectual property provider CAST, Inc. has successfully undergone functional and interoperability testing at two recent multi-vendor plugfests in Germany: the Industrial Internet Consortium (IIC) TSN Plugfest July 24–27, 2018, in Stuttgart, and the Labs Network Industry 4.0 e.V. (LNI) Plugfest August 22–23, 2018, in Augsburg.

At these plugfests, engineers from Fraunhofer IPMS successfully added their reference design for a TSN end node device to an Ethernet network integrating TSN switches and endpoints from several independent vendors. The resulting TSN testbeds mimic real-world industrial and automotive environments with a diverse mix of real-time signal scheduling and priority challenges that must be satisfactorily managed by the system. The Fraunhofer IPMS design operated successfully, with respect to both its own functionality and in effective cooperation with the rest of each TSN testbed.

Engineers from fifteen firms participate in the LNI Time Sensitive Networking Ethernet Plugfest in Augsburg, Germany August 22, 2018.

“Participating in these plugfests enabled us to rigorously exercise our TSN endpoint design in two different real-world-like environments, each networking our design with switches and end nodes from all the other leading TSN developers,” said Frank Deicke, business unit manager for Wireless Microsystems at Fraunhofer IPMS. “We found that our design performed extremely well and is definitely market-ready, while also gaining insights that will help our customers have even smoother TSN deployment experiences.”

About the Plugfests

Fraunhofer IPMS is a member of the Industrial Internet Consortium (IIC), and participated in the IIC TSN Plugfest that took place July 24–27, 2018, in Stuttgart, Germany. The testing there focused on two of the IEEE TSN standards: IEEE 802.1as Time Synchronization, and IEEE 802.1Qbv Time Aware Traffic Scheduling. Twenty firms contributed TSN designs, significantly enlarging the IIC TSN Testbed, which will serve as the foundation for future testing. Learn more about the IIC TSN program at www.iiconsortium.org/time-sensitive-networks.htm.

Fraunhofer also participated in the TSN plugfest conducted by Labs Network Industry 4.0 e.V. (LNI) on August 22–23, 2018, in Augsburg, Germany. Fifteen firms integrated their switch and end node designs across an Ethernet network for rigorous functional and interoperability testing. Learn more about LNI’s Ethernet TSN efforts at www.lni40.de.

About TSN and the Ethernet Subsystem

The IEEE TSN Ethernet standards manage challenging networks having a mix of critical and non-critical nodes and have helped Ethernet emerge as the preferred bus for today’s complex industrial and automotive buses. TSN ensures that quality of service requirements are satisfied by prioritizing and scheduling diverse network traffic while also providing ultra-low and deterministically-constrained latency where needed.

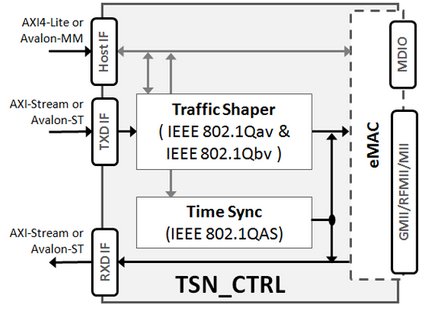

Fraunhofer IPMS’ entry to the plugfests is a 1000 Mbps endpoint FPGA board based on a reference design for the TSN_CTRL Ethernet Subsystemalready available from CAST. That Subsystem combines three essential IP cores:

- the Time Synchronizerimplements IEEE 802.1AS to automatically synchronize local and system time and generate timestamps and alerts needed for time-aware nodes and applications;

- the Traffic Shaperimplements IEEE 802.1Qav and 802.1Qbv to provide bandwidth allocation and time multiplexing for up to eight traffic classes, ensuring sufficiently low latency and minimum jitter as required; and

- a specially-designed Ethernet MACwith ultra-low latency provides standards-based Ethernet functionality that works well with TSN.

The company believes this is the first commercially-available IP subsystem implementing the latest TSN standards, and has already licensed it to multiple customers.

Block diagram showing the major elements of the TSN Ethernet Subsystem IP available from CAST.

About Fraunhofer IPMS and CAST

The Fraunhofer Institute for Photonic Microsystems (IPMS) is a Dresden, Germany based research and development group focused on integrated circuits, microsystems (MEMS/MOEMS), nanoelectronicsand optical sensors and actuators. Learn more at www.ipms.fraunhofer.de.

CAST, Inc. is an experienced silicon IP supplier offering a range of compression solutions and image processing functions; 8051 microcontrollers and extreme-low-power 32-bit BA2X™ processors; and a variety of peripherals, interfaces, security, and other IP cores. CAST IP features easy integration and reuse, straightforward licensing, and availability for ASICs or FPGAs from all leading silicon providers. Learn more by visiting www.cast-inc.com, emailing info@cast-inc.com, or calling +1 201.391.8300.

Related Semiconductor IP

- ASIL B Compliant MIPI CSI-2 CSE2 Security Module

- SHA-256 Secure Hash Algorithm IP Core

- EdDSA Curve25519 signature generation engine

- DeWarp IP

- 6-bit, 12 GSPS Flash ADC - GlobalFoundries 22nm

Related News

- CAST Releases TSN Ethernet Subsystem for Automotive and Industrial Applications

- CAN to TSN Gateway from CAST Bridges CAN 2.0/FD Buses with Time Sensitive Ethernet

- CAST Adds Switched TSN Endpoint Controller to Time-Sensitive Networking Ethernet IP Cores Family

- CAST Introduces Ultra-Low Latency TSN Ethernet Switch IP Core

Latest News

- Analog Bits Demonstrates Real-Time On-Chip Power Sensing and Delivery on TSMC N2P Process at TSMC 2026 Technology Symposiums

- TES offers a High-Frequency Synthesizer and Clock Generator IP for X-FAB XT018 - 0.18µm BCD-on-SOI technology

- Faraday Delivers IP Solutions to Enable Endpoint AI Based on UMC’s 28nm SST eFlash

- AiM Future Partners with Metsakuur Company to Commercialize NPU-Integrated Hardware

- ESD Alliance Reports Electronic System Design Industry Posts $5.5 Billion in Revenue in Q4 2025