The Semiwise's Flat Field Transistor enables the continuation of DRAM scaling

March 24, 2022 -- The Flat Field Transistor (FFT) developed by Semiwise offers a solution to the DRAM scaling problems improving dramatically the margins of the DRAM sense amplifiers.

Although the DRAM cell transistors have undergone a dramatic revolution from recess gate to saddle FinFET, for cost reasons, the DRAM sense amplifiers and periphery continue to be manufactured using conventional bulk MOSFETs.

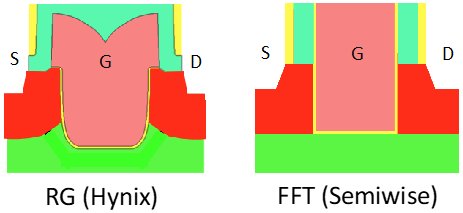

However, with the relentless scaling of the DRAM cell the margins of the sense amplifier (SA) dramatically decrease. The statistical variability (mismatch) of the bulk MOSFETs is the main factor eroding the SA margins. The addition of offset compensation circuits to the SA, adopted by most of the DRAM manufacturers, increases the SA related ‘dark’ area on the DRAM chips, further eroding the DRAM scaling. Recently Hynix has introduced recess gate (RG) SA transistors to tackle the DRAM SA statistical variability problem at increased manufacturing complexity and costs, and reduced performance.

Fig. 1 Comparison between the Hynix RG transistor and the Semiwise FFT

The FFT developed by Semiwise can deliver more than 50% reduction of the statistical variability compared to bulk MOSFETs with identical dimensions. This is complemented by 30% performance increase and 5% reduction of the manufacturing costs compared to the equivalent bulk CMOS technology transistors. More details about the FFT technology and performance are available here

The advantages of the FFT can be sustained down to 22nm bulk CMOS offering long-term DRAM scaling solution. The Semiwise analysis shows that at 22nm bulk CMOS, the FFT delivers more than 50% reduction in the SA offset variability. This can be translated to more than 4 time reduction in the FFT SA area compared to the bulk MOSFET SA at identical offset variability distributions.

The CEO of Semiwise Prof. Asenov commented: “In the last 20 years I have been focusing my attention to the modeling and simulation of statistical variability in contemporary and future CMOS technologies. Simulation tools developed in my research group and former company, Gold Standard Simulations, are now in the heart of the Synopsys variability aware Design Technology Co-Optimisation (DTCO) flow. I am delighted that the use of these technology and tools has enabled Semiwise to develop the FFT technology that can revolutionizes the DRAM scaling.”

About Semiwise:

Semiwise develops innovative low-power CMOS transistor-level IP that improves performance and variability, and drastically reduces power consumption. Semiwise also offers simulation services and consulting to the semiconductor industry including fabless, IEDM and foundry players. The CEO of Semiwise, Professor Asenov was the founder of Gold Standard Simulations (GSS), a 2010 start-up from the University of Glasgow which developed the first TCAD based Design-Technology Co Optimisation (DTCO) tool chain. After the acquisition of GSS by Synopsys in 2016 the TCAD-to-Spice technology originally developed by GSS is now part of the Synopsys TCAD offering in the so called TCAD-to-Spice flow . This technology was used in the development of the FFT.

Related Semiconductor IP

- SHA-256 Secure Hash Algorithm IP Core

- EdDSA Curve25519 signature generation engine

- DeWarp IP

- 6-bit, 12 GSPS Flash ADC - GlobalFoundries 22nm

- LunaNet AFS LDPC Encoder and Decoder IP Core

Related News

- QuickLogic QuickMIPS ESP Is Industry's First -- Combines a High-speed Processor With Hardwired Functions and Field Programmability

- ARM's Q4 sales flat, but company bullish for 2001

- Silicon Access, SandCraft raise stakes in network processor field

- Solutions to CMOS scaling limits are appearing, conference hears

Latest News

- BrainChip Unveils Radar Reference Platform to Bridge the ‘Identification Gap’ in Edge AI

- Siemens accelerates AI chip verification to trillion‑cycle scale with NVIDIA technology

- SiFive Raises $400 Million to Accelerate High-Performance RISC-V Data Center Solutions; Company Valuation Now Stands at $3.65 Billion

- IntoPIX Unleashes Zero‑Latency IP Video Streaming With JPEG XS, IPMX & SMPTE 2110 At NAB Show 2026

- OPENEDGES Advances Commercialization of LPDDR6/5X Memory Subsystem IP, Targeting Next-Generation AI and HPC Markets