RISC-V in AI and HPC Part 1: Per Aspera Ad Astra?

By Anton Shilov, EETimes (January 6, 2025)

Introduced in 2014, the RISC-V instruction set architecture has been evolving at a pace that Arm and x86 ISAs have never experienced. Initially, RISC-V cores were used solely for microcontrollers and applications that did not require high performance, but rather benefited from low cost and low power. Since RISC-V is an open-source architecture, it quickly gained popularity among dozens and then hundreds of companies, each of which contributed to further development of the ISA.

Introduced in 2014, the RISC-V instruction set architecture has been evolving at a pace that Arm and x86 ISAs have never experienced. Initially, RISC-V cores were used solely for microcontrollers and applications that did not require high performance, but rather benefited from low cost and low power. Since RISC-V is an open-source architecture, it quickly gained popularity among dozens and then hundreds of companies, each of which contributed to further development of the ISA.

Nowadays, there are tiny RISC-V cores suitable for microcontrollers and DSPs, more advanced cores suitable for SSD controllers, Linux-capable cores for embedded applications, specialized cores that can be used for AI workloads, and “fat” cores that can serve data center and high-performance computing (HPC) applications.

In fact, since the RISC-V technology is so versatile and easily customizable by chip designers, it is very well suitable for AI and HPC applications that are developing very rapidly these days. It can take years to add support for a data format to an x86 or Arm microarchitecture because both ISAs are controlled by essentially three companies: AMD and Intel when it comes to x86 and Arm Holdings when it comes to Arm.

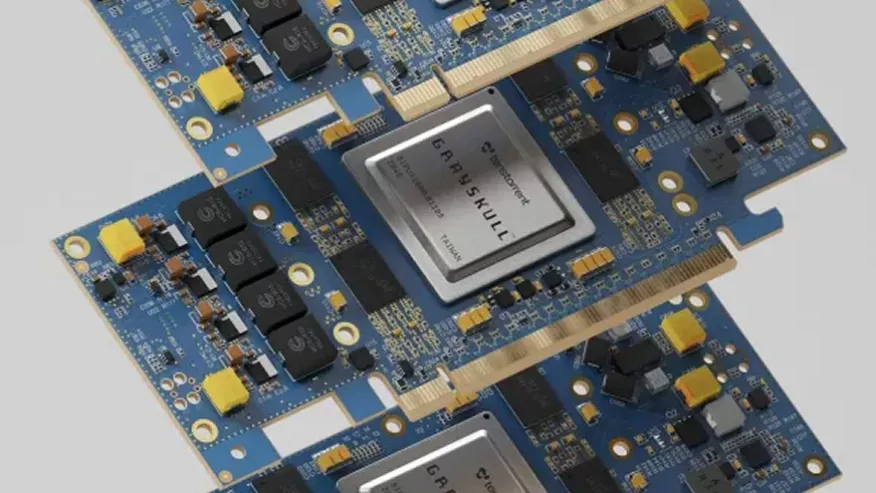

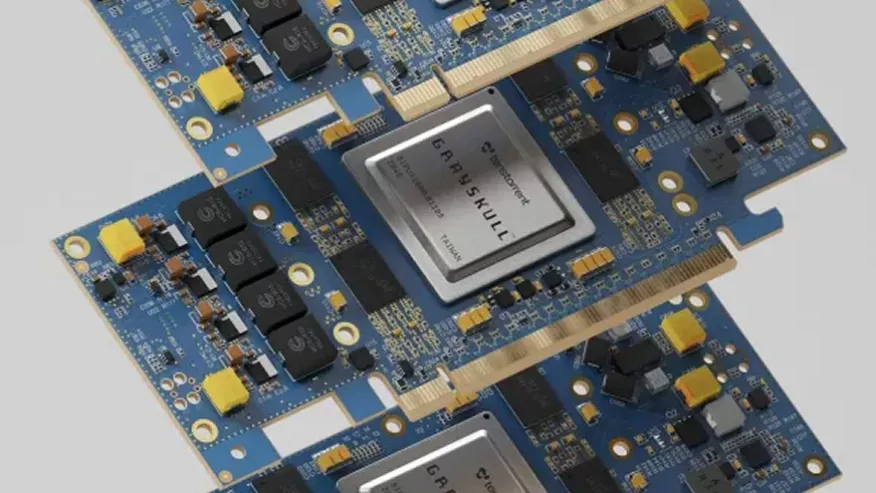

Yet, companies like Red Semiconductor, SemiDynamics, SiFive, Tenstorrent, MIPS, and Ventana Micro tend to advance their cores in terms of supported data formats and instructions much faster than anyone in the x86 or Arm worlds.

While RISC-V has yet to see its strategical infliction point in AI and HPC realms, it looks like the ISA has a lot of chances to get widespread adoption in market segments that benefit a lot from maximum cost-efficiency, flexibility, customizability and reduced dependency. Analysts do not expect RISC-V to gain a significant AI and HPC market share over the next few years, though it is entirely possible that the ISA will get much more widespread in the longer term.

In this first article of a three-part series, we had a chance to talk with analysts and developers of various RISC-V processors, including those who design general-purpose CPU IP cores and application-specific accelerator IPs, about RISC-V’s prospects in AI and HPC market segments as they are seen today.

To read the full article, click here

Related Semiconductor IP

- RISC-V IOPMP IP

- RISC-V Debug & Trace IP

- Gen#2 of 64-bit RISC-V core with out-of-order pipeline based complex

- 64-bit RISC-V core with in-order single issue pipeline. Tiny Linux-capable processor for IoT applications.

- Tiny, Ultra-Low-Power Embedded RISC-V Processor

Related News

- Eliyan Secures $50 Million in Strategic Investments from Leading Hyperscalers and AI Infrastructure Providers to Accelerate Scalable AI Systems

- Chinese RISC-V Chipmaker SpacemiT Launches K3 AI CPU, Highlighting the Rise of Open-Source Hardware in Intelligent Computing

- Phison Selects Andes RISC-V Cores for its First aiDAPTIV+ AI Solution, Marking a Major Milestone in AI Architecture

- Cadence Unleashes ChipStack AI Super Agent, Pioneering a New Frontier in Chip Design and Verification

Latest News

- GUC Announces 3nm 12 Gbps HBM4 PHY and Controller

- Arasan acheives the Industry's First ASIL-D Certification for its CAN XL IP Core

- Quintauris and Elektrobit Partner to Enable Reliable RISC-V Solutions for Automotive

- Wind River Joins the CHERI Alliance and Collaborates with Innovate UK to Accelerate Cybersecurity Innovation

- Arteris and MIPS Partner to Accelerate Development for Physical AI Platforms