Quadric's DevStudio Speeds Software Development with Industry's First Integrated ML + DSP Cloud-Based Code Development Platform

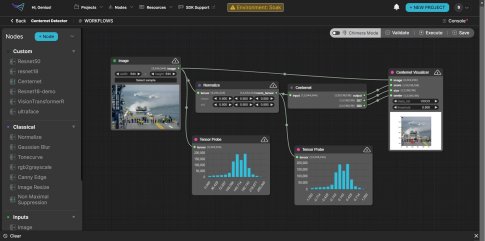

BURLINGAME, Calif. -- May 22, 2023 -- Quadric today introduced the Quadric Developer Studio, an online collaborative development environment for ChimeraTM general purpose neural processing unit (GPNPU) processors. Quadric DevStudio speeds software development with the industry’s first integrated machine learning (ML) plus digital signal processing (DSP) development system. This comprehensive environment provides users with a graphical interface for constructing complex signal chains mixing classic C++ code plus neural net graph code, uploading and compiling machine learning ONNX graphs, uploading and compiling C++ code, and simulating entire workloads. Until now, most neural processing units (NPUs) used for artificial intelligence (AI) have been hard-coded inflexible hardware, and any programming changes had to be offloaded to a much slower DSP or CPU core.

A significant advantage of Quadric DevStudio is that neural network graphs and C++ code are merged into a single, fully programmable software application. Only one tool chain is required for scalar, vector, and matrix computations. Memory bandwidth is optimized by a unified compilation stack that helps result in significant power minimization. Future code changes can easily be made later as new features are added by the application developers.

Underlying the new DevStudio is the Chimera Software Development Toolkit (SDK) which includes the groundbreaking Chimera Graph Compiler (CGC), the Chimera Instruction Set Simulator (ISS), an LLVM-based C++ compiler, and the Chimera Compute Library (CCL) – a comprehensive set of building block libraries and APIs that speeds creation of optimized code for the Chimera processor.

Software developers and SoC architects can use DevStudio to link, compile and profile complex signal chains using a combination of pre-built C++ functions, pre-compiled neural networks, and user uploaded code.

Quadric’s DevStudio also enables sharing of application code both within and across organizations. “Our DevStudio is designed to serve as a code sharing platform within the ecosystem of developers and users of Chimera-powered silicon,” noted Daniel Firu, co-founder and Chief Product Officer at Quadric. “Teams can consist of individuals within one organization or can span company boundaries, thus enabling rapid solution development in a secure, cloud-hosted environment.”

Chimera GPNPUs Now Available

The Chimera family of GPNPUs is a semiconductor intellectual property (IP) offering that blends the ML performance characteristics of a neural processing accelerator with the full C++ programmability of a modern DSP. Chimera GPNPUs provide one unified architecture for ML inference plus pre-and-post processing, greatly simplifying both system-on-chip (SoC) hardware design by the semiconductor developer today and subsequent software programming months and years later by application developers.

Announced in November 2022, the Chimera GPNPUs are released and have been delivered to early licensees. Now the introduction of Quadric’s DevStudio provides easy cloud access to the Chimera SDK and CGC compiler for both chip design teams contemplating new SoC architectures as well as application code developers who can start building and tuning complete signal chain code purely in the cloud before target silicon is available.

High Convolution Efficiency + Custom Operator Support

The Chimera GPNPU architecture excels at convolution layers, the heart of convolutional neural networks (CNNs). Quadric Chimera cores deliver ML inference performance similar to the efficiency of dedicated CNN offload engines but with full programmability. Unlike conventional accelerators that can only run a handful of predetermined ML operators, Chimera GPNPUs can run any ML operator. Custom operators can be added by the software developer simply by writing a C++ kernel utilizing the Chimera CCL application programming interface then compiling that kernel using the Chimera SDK. DevStudio quickens the process of importing ONNX network graphs, compiling to identify new or problematic NN operators, creating C++ kernels for previously unknown ops, and linking the new ops with code generated by CGC. Operators added with the Chimera SDK flow can be highly performant, utilizing the full compute capability of the Chimera GPNPU.

Competing architecture solutions rely upon conventional CPUs or DSPs as the “fallback” programable solution for newly emergent ML operators, but those CPUs or DSPs are 10x to 1000x lower performing than the accelerators with which they are paired so performance is significantly degraded.

Limited Beta Ready for Evaluation

Quadric DevStudio is available today for a limited set of beta users. Visit studio.quadric.io to request access. For more information and details on the Chimera architecture visit the www.quadric.io website.

About Quadric

Quadric Inc. is the leading licensor of general-purpose neural processor IP (GPNPU) that runs both machine learning inference workloads and classic DSP and control algorithms. Quadric’s unified hardware and software architecture is optimized for on-device ML inference. Learn more at www.quadric.io.

Related Semiconductor IP

- EdDSA Curve25519 signature generation engine

- DeWarp IP

- 6-bit, 12 GSPS Flash ADC - GlobalFoundries 22nm

- LunaNet AFS LDPC Encoder and Decoder IP Core

- ReRAM NVM in DB HiTek 130nm BCD

Related News

- Quadric Announces $21M to Advance Its Disruptive Edge AI Platform

- Quadric Appoints Former Arm Vice President Steve Roddy as Chief Marketing Officer and Accelerates the Licensing of Its GPNPU Architecture

- Quadric and MegaChips Form Partnership to Bring IP Products to ASIC and SoC Market

- Quadric Appoints Former Cadence VP Dhanendra Jani as New VP of Engineering

Latest News

- Codasip announces strategic pivot and divestiture

- UMC Reports Sales for March 2026

- Semidynamics Secures a Strategic Investment to Advance Memory-Centric AI Inference Chips

- Ultra Accelerator Link™ (UALink™) Consortium Publishes Four Specifications Defining In-Network Compute, Chiplets, Manageability and 200G Performance

- GUC Monthly Sales Report – March 2026