IPrium releases DVB-CID Demodulator

December 02, 2014 - FPGA intellectual property (IP) provider IPrium LLC today announced that it has expanded its family of Demodulator IP products with a new DVB-CID Demodulator IP Core for the ETSI Carrier identification (CarrierID) standard.

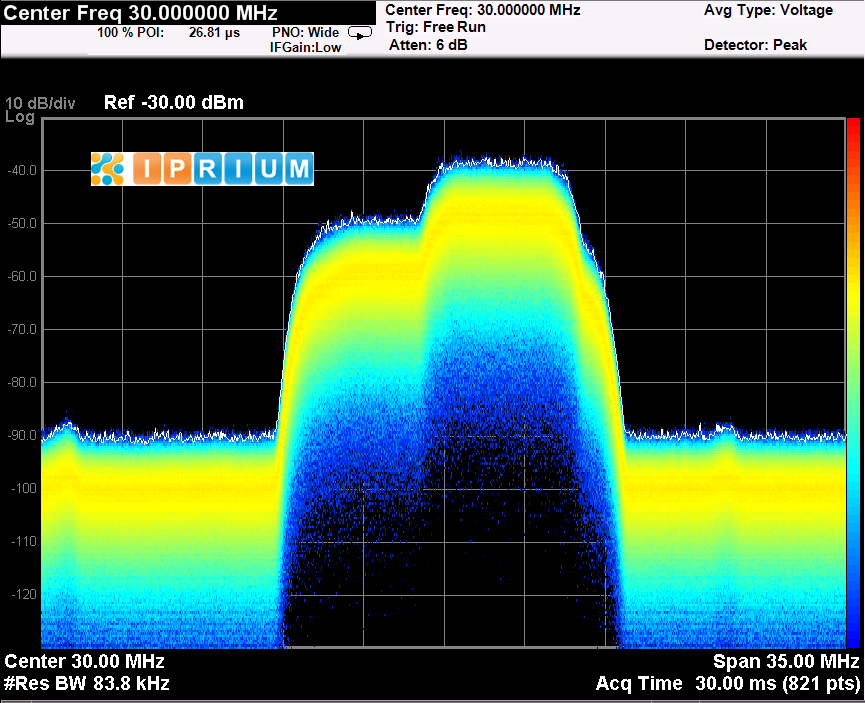

The DVB-CID Demodulator IP Core is high performance, wide bandwidth digital solution for detection and identification of CID carrier in RFI cases. The IP Core has been silicon-proven using multiple development boards and is compliant with ETSI TS 103 129 (as of v.1.1.1 05/2013) "Framing structure, channel coding and modulation of a carrier identification system (DVB-CID) for satellite transmission" standard.

The IP Core supports blind scan algorithm which can be used to extract CID even when interferer is 10 dB below carrier spectrum. The blind scan algorithm works across the full bandwidth of any satellite carrier.

Pricing and Availability

The DVB-CID Demodulator IP Core is available immediately in synthesizable Verilog or optimized netlist format, along with synthesis scripts, simulation test bench with expected results, and user manual. For further information, product evaluation, or pricing, please visit the IP Core page:

Related Semiconductor IP

Related News

- IPrium releases PSK Demodulator

- IPrium releases SOQPSK-TG Demodulator for Aerospace Telemetry

- Sarnoff ClearLoc(TM) VSB/QAM Demodulator Adds Digital/HDTV, Cable Capabilities To Receivers

- Silicon Hive, a semiconductor IP supplier in the Philips Technology Incubator, Demonstrates World's First Fully Programmable Digital TV Demodulator IP Core

Latest News

- Hardware Root of Trust Essential for AI Chip Integrity

- AI Compute Demand Drives 44% YoY Growth for Top 10 Global Fabless IC Firms in 2025

- IBM Announces Strategic Collaboration with Arm to Shape the Future of Enterprise Computing

- Rambus Unveils HBM4E Controller: 16 GT/s, 2,048-Bit Interface, Enabling C-HBM4E

- AimFuture, a Leader in Home Appliance NPUs, to Integrate Mesacure Company’s AI Algorithms