intoPIX Showcases a SMPTE2022 Reference Design running on Xilinx FPGA and enabling Live Video over IP transport using JPEG2000

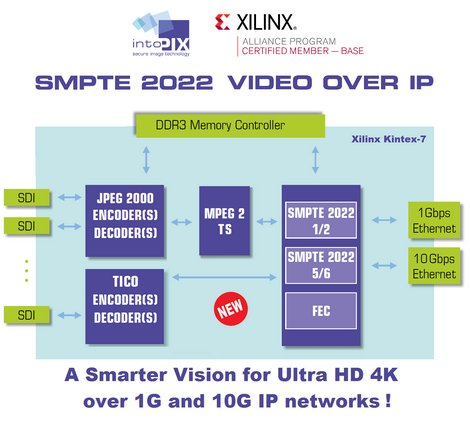

Belgium, Mont-Saint-Guibert -- April 4, 2014– intoPIX has today officially released its smart SMPTE2022 video over IP reference design based on Xilinx FPGAs. For this reference design, intoPIX has developed a new MPEG2-TS encapsulation layer for their JPEG2000 compression IP-core and has co-integrates the Xilinx SMPTE2022-1/2 IP-core.

intoPIX provides a reference design that follows VSF Technical Recommendation, “Transport of JPEG 2000 Broadcast profile video in MPEG-2 TS over IP”, facilitating the FPGA integration, guaranteeing interoperability and accelerating the time to market, all being integrated in a single Xilinx Kintex 7 FPGA.

“intoPIX brings a cost-effective and smart way to build a video over IP solution for HD or even 4K over 1G networks using a JPEG2000 visually lossless compression that offers an ultra-latency going below 10ms” said Gael Rouvroy, intoPIX CTO.

“It is also planned by intoPIX and Xilinx to integrate the TICO lightweight compression in current SMPTE2022-5/6 reference design and map up to three 4K streams over 10G with only few pixel lines of latency. Incredibly small in FPGA with no needs of external memory, the intoPIX light compression is a key alternative to uncompressed video transport to migrate Broadcast infrastructure to 4K” said Robert Green, Sr. Manager, Xilinx Broadcast & Professional A/V Business Segment.

intoPIX Xilinx Kintex-7 JPEG2000 SMPTE2022 video-over-IP reference design will be showcased at NAB tradeshow next week in Las Vegas at intoPIX (C5243) booth.

Related Semiconductor IP

Related News

- intoPIX, Adeas, and Nextera to showcase Reference design on IPMX at ISE 2022 on Xilinx Booth

- intoPIX and Macnica Americas Demonstrate 4K Future-proof and Interoperable SMPTE2022 JPEG2000 Video Over An IP FPGA Reference Design at NAB 2014

- Renesas Electronics Collaborates with Xilinx on Versal ACAP Reference Designs

- Xilinx and Spline.AI Develop X-Ray Classification Deep-Learning Model and Reference Design on AWS

Latest News

- Silicon Creations Celebrates 20 Years of Global Growth and Leadership in 2nm IP Solutions

- TSMC Debuts A13 Technology at 2026 North America Technology Symposium

- Cadence Collaborates with TSMC to Accelerate Design of Next-Generation AI Silicon

- Synopsys Partners with TSMC to Power Next-Generation AI Systems with Silicon Proven IP and Certified EDA Flows

- JEDEC® Previews LPDDR6 Roadmap Expanding LPDDR into Data Centers and Processing-in-Memory