Codasip boosts Studio processor design tools with AXI automation

Munich Germany, October 26, 2021 – Codasip, the leading supplier of customizable RISC-V processor IP, today announced further enhancements to its Studio processor design toolset. New features in Studio 9.1 include an expanded bus support with full AXI for high-performance designs, as well as improved support for LLVM and improved code density.

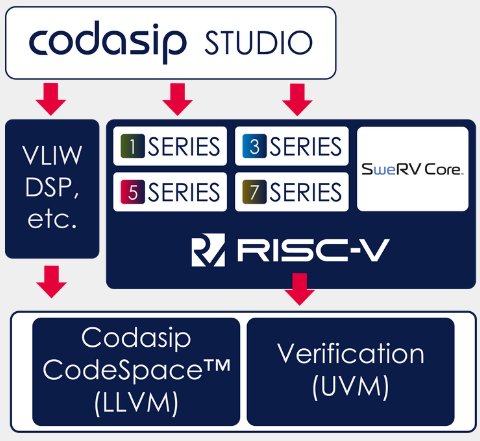

Studio is at the heart of Codasip’s offering to simplify the task of customizing designs, enabling companies of all sizes to differentiate their products at the core. Studio has been the market leader in democratizing processor design since it was launched in 2014. Simplifying processor customization, Studio walks designers through the steps necessary to create their ideal custom RISC-V processor from a Codasip embedded or application core design – ensuring the design achieves predictable results and the highest performance.

Studio delivers these benefits to a rapidly expanding community of RISC-V developers around the world and, with today’s launch of Studio 9.1, will extend this leadership enabling higher-performance and lower cost designs.

Specifically in 9.1, Studio users gain access to additional bus interfaces, to now include full AXI which means Studio will readily support the development of more powerful application cores and multi-core systems.

Instruction memory size can dominate cost in embedded processors so code density improvements in Studio 9.1 will help to contribute to reducing overall system costs.

Codasip’s latest update incorporates the LLVM-based SDK (the fast C/C++ compiler, Linker Support Package – all of which were incorporated as part of Studio 9.0 launched in April 2021). This update significantly improves support for custom instructions in application cores running a rich OS, such as GNU/Linux. Another new feature brings support for ISA sub-targets that hugely reduce the maintenance of different SDKs for different ISA configurations.

Zdenēk Prikryl, Codasip CTO, said, “We are constantly evolving our tools offering and due to the nature of the diverse customer types, our projects and developments continue to help push our design tools further. Codasip is keen to simplify design for differentiation with our processor cores and tools which we have developed to make it easy for designers of any size to benefit from: enabling them to get high-performance, cost-effective and (importantly!) significantly differentiated products to market quickly and easily.”

Related Semiconductor IP

- RISC-V Debug & Trace IP

- Gen#2 of 64-bit RISC-V core with out-of-order pipeline based complex

- Compact Embedded RISC-V Processor

- Multi-core capable 64-bit RISC-V CPU with vector extensions

- 64 bit RISC-V Multicore Processor with 2048-bit VLEN and AMM

Related News

- Codasip Releases Studio 8, a Breakthrough in RISC-V Automation, and the Bk7 RISC-V Processor Core for Real-Time Computing Applications

- Rambus Selects Codasip Studio for SDK Development of RISC-V Processor

- Codasip Announces Studio 7, Design and Productivity Tools for Rapid Generation of RISC-V Processors

- Codasip and Metrics Design Automation Announce the Integration of the Metrics Cloud Simulation Platform in Codasip's RISC-V SweRV CORE Support Package Pro

Latest News

- Alchip Appoints Freddy Engineer Chief Business Officer and North America General Manager

- Perceptia Devices and Dolphin Semiconductor Partner to Deliver Best-in-Class IP Portfolio Covering Power Management, Clocking, High-Quality Audio and In-Situ Monitoring

- TSMC Chases Soaring AI Demand

- EU DARE Project Is Scrambling to Replace Codasip

- Sofics and Alcyon Photonics Partner to Support Next-Generation Photonic Systems