Agile Analog launches innovative digitally wrapped analog IP subsystems

Significantly reducing analog IP integration effort and costs

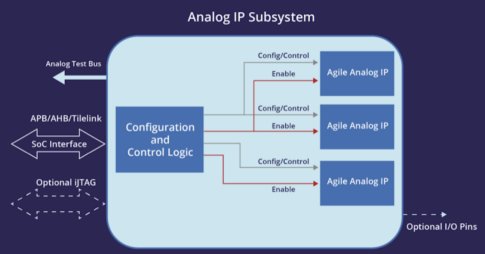

Cambridge, UK -- April 25, 2023 -- Agile Analog, the customizable analog IP company, has launched its first range of analog subsystems, covering power management, PVT sensing, and sleep management. These innovative, digitally wrapped subsystems significantly reduce the effort required to integrate multiple analog IPs into any ASIC by allowing the IP to be dropped straight into a digital design flow and connected via a standard peripheral bus, such as AMBA APB. The subsystems look just like a normal block of digital IP with the standard interfaces that engineers would expect, making them easy to understand and handle. As a result, time to market, costs and risk are radically reduced. Initially, the company is introducing three subsystems: agilePMU for power management, agilePVT - PVT sensor, and agileSMU for sleep management.

Chris Morrison, Director of Product Marketing at Agile Analog, said, “I’m delighted to announce our first three subsystems. Customers are always looking for ways to reduce time to market, cost, and risk, and our new, digitally wrapped subsystems do just that. Crucially, customers no longer need to deal with the complex mixed-signal boundary between analog and digital, drastically decreasing their design effort and the risks often associated with integrating a complex array of analog IP.”

The IP blocks within a subsystem are all from Agile Analog’s existing portfolio of customizable analog IP. This allows each block within the subsystem to be customized to the customer’s exact requirements whilst sitting within the overall digital wrapper. As with all Agile Analog IP, the digitally wrapped subsystems are process and foundry agnostic, and each design is optimized for the customer’s specific PDK. Integrating IP within a subsystem further enhances the customer’s design by removing duplicate analog functions, reducing design rule checking (DRC) requirements, and optimizing interconnects. These lead to increased noise immunity, lower power consumption and smaller area.

Another key benefit to the customer is that all the verification requirements of the analog to digital, mixed-signal, boundary are performed by Agile Analog. This significantly reduces the customer design and verification time, de-risks the design process, lowers the cost of licensing mixed signal design tools, and simplifies integration. Customers can now add analog features to provide product differentiation without needing specialist analog and mixed signal engineers, and the associated costly toolchain.

Agile Analog’s subsystems are supplied with a full set of supporting collateral, including System Verilog models for easy integration into customers’ existing digital verification flows.

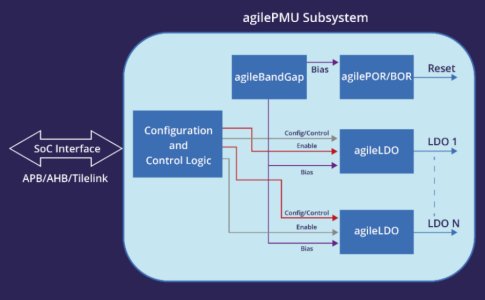

agilePMU Power Management Subsystem

The agilePMU Subsystem is an efficient and highly integrated power management unit for SoCs/ASICs. Featuring a power-on-reset, multiple low drop-out regulators, and an associated reference generator. The agilePMU Subsystem is designed to ensure low power consumption while providing optimal power management capabilities. Equipped with an integrated digital controller the agilePMU Subsystem offers precise control over start-up and shutdown, supports supply sequencing, and allows for individual programmable output voltage for each LDO. Status monitors provide real-time feedback on the current state of the subsystem, ensuring optimal system performance.

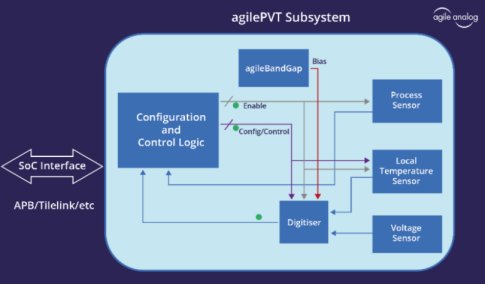

agilePVT Sensor Subsystem

The monitoring of process, voltage and temperature variations are critical to optimize power and performance for modern SoCs/ASICs, especially for advanced node and FinFET processes. The agilePVT Sensor Subsystem is a low power integrated macro consisting of process, voltage, and temperature sensors, and an associated reference generator, for on-chip monitoring of a devices’ physical, environmental, and electrical characteristics. Equipped with an integrated digital controller the agilePVT Subsystem offers precise control over start-up and shutdown. Status monitors provide real-time feedback on the current state of the subsystem, ensuring optimal system performance over the full product lifecycle.

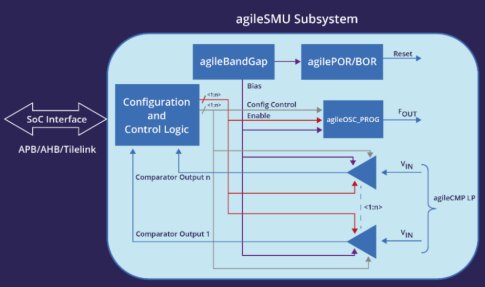

agileSMU Sleep Management Subsystem

The agileSMU Subsystem is a low power integrated macro consisting of the essential IP blocks required to securely manage waking up a SoC from sleep mode. Typically containing a programmable oscillator for low frequency SoC operation and RTC, a number of low power comparators which can be used to initiate the wake-up sequence, and a power-on-reset which provides a robust, start-up reset to the SoC. Equipped with an integrated digital controller the agileSMU Subsystem offers precise control over wake-up commands and sequencing. Status monitors provide real-time feedback on the current state of the subsystem, ensuring optimal system performance over the full product lifecycle.

Agile Analog www.agileanalog.com

Agile Analog is transforming the world of analog IP with Composa™, its innovative, configurable, multi-process analog IP technology. Headquartered in Cambridge, UK, with a growing number of partners and customers across the globe, Agile Analog has developed a unique way to automatically generate analog IP that meet the customer’s exact specifications on almost any process from any foundry. The company provides a wide and ever expanding selection of analog IP and subsystems for power management, data conversion, IC health and monitoring, security and always-on domains. Agile Analog's novel approach utilises tried and tested analog circuits within its Composa library to create customised and verified analog IP solutions. This reduces the time to market and increases quality, helping to accelerate innovation in semiconductor design.

Related Semiconductor IP

- ASIL B Compliant MIPI CSI-2 CSE2 Security Module

- SHA-256 Secure Hash Algorithm IP Core

- EdDSA Curve25519 signature generation engine

- DeWarp IP

- 6-bit, 12 GSPS Flash ADC - GlobalFoundries 22nm

Related News

- Analog IP supplier Agile Analog builds footprint in Asia-Pacific with new sales and engineering operation based in Taiwan

- RISC-V startup recruits former Agile Analog CEO Ramsdale

- Global sectoral demand encourages Agile Analog to locate in Scotland

- Using Agile Analog's process-agnostic Analog IPs can help solve current Semiconductor capacity challenges

Latest News

- Analog Bits Demonstrates Real-Time On-Chip Power Sensing and Delivery on TSMC N2P Process at TSMC 2026 Technology Symposiums

- TES offers a High-Frequency Synthesizer and Clock Generator IP for X-FAB XT018 - 0.18µm BCD-on-SOI technology

- Faraday Delivers IP Solutions to Enable Endpoint AI Based on UMC’s 28nm SST eFlash

- AiM Future Partners with Metsakuur Company to Commercialize NPU-Integrated Hardware

- ESD Alliance Reports Electronic System Design Industry Posts $5.5 Billion in Revenue in Q4 2025