video processing IP

Filter

Compare

246

IP

from

52

vendors

(1

-

10)

-

Specialized Video Processing NPU IP

- High Performance and Minimum DRAM Bandwidth by Line-by-Line Processing

- 4x ~10x times faster processing by reducing DRAM access

- Small Area and High utilization by Fully Programmable Processing Core

-

Video Processing Subsystem

- AXI Stream input and output interface

- Video resolutions up to UHD@60 fps (both at input & output interface)

- Features high quality Multi-tap poly-phase Scaler, Motion adaptive deinterlacer, Color space conversion, Chroma resampling, Letter box functions

- Video encoding RGB 4:4:4, YUV4:4:4, YUV 4:2:2 and YUV 4:2:0)

-

Video Post Processing IP (cropping, color space conversion (CSC), alpha blending, 3D LUT, and flexible resizing)

- The PC820 pixel processor is an IP which provides pixel processing functions such as cropping, color space conversion (CSC), alpha blending, 3D LUT, and flexible resizing.

- It supports input data of various compressed or uncompressed RGB and YUV formats.

- After being processed by the pixel processor, the data can be output in uncompressed, compressed, or normalized formats.

-

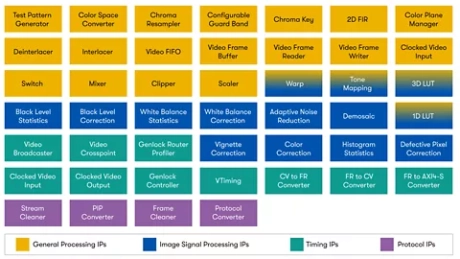

Video and Vision Processing Suite

- The Intel® FPGA Video and Vision Processing Suite is a collection of next-generation Intel® FPGA intellectual property (IP) functions that you can use to facilitate the development of custom video and image processing designs

- These Intel® FPGA IP functions are suitable for use in a wide variety of image processing and display applications, such as studio broadcast, video conferencing, AV networking, medical imaging, industrial inspections and robotics, smart city/retail and consumer.

-

Video and Image Processing Suite

- The Intel FPGA Video and Image Processing Suite is a collection of Intel FPGA intellectual property (IP) functions that you can use to facilitate the development of custom video and image processing designs

- These Intel FPGA IP functions are suitable for use in a wide variety of image processing and display applications, such as studio broadcast, video conferencing, AV networking, medical imaging, smart city/retail, and consumer.

-

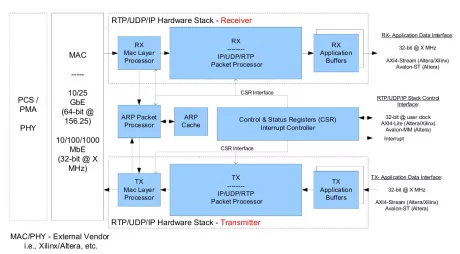

RTP/UDP/IP Protocol Hardware Stack – H.264/H.265 NAL Video Streams Packet Processing

- RTP/UDP/IP Protocol Hardware Stack, targets H.264 NAL Streams. See DB RTP-UDP-IP-AV for raw, uncompressed RGB/YUV video streams

- For RX (i.e., receiving packets from the network), there is optional packet reordering to absorb network jitter.

- For both TX/RX, multiple NAL video streams supported. The DB-RTP-UDP-IP-NAL targets H.264 NAL Streams.

-

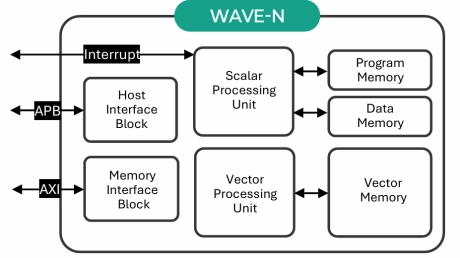

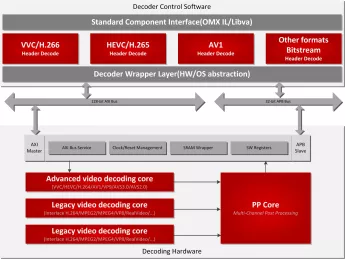

Microprocessor IP for video codecs and video processing -- High Number of Streams Decoder For Data Center

- Enables up to 256 streams decoding with robustness, high throughput single-core solution, or multi-core solution, supporting VVC, AV1, HEVC, H.264, AVS3, AVS2, VP9 video formats, JPEG, and legacy formats.

-

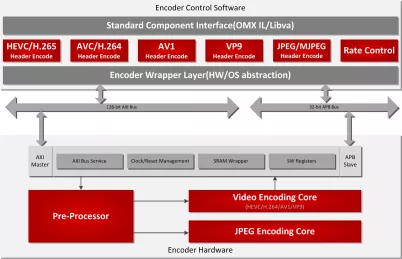

Microprocessor IP for video codecs and video processing -- High Number of Streams Encoder For Data Center

- Enables up to 256 streams encoding with high video quality single-core solution, or multi-core solution, supporting AV1, HEVC, H.264, VP9 video formats and JPEG.

-

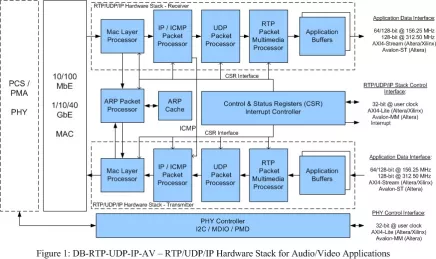

RTP/UDP/IP Protocol Hardware Stack – Raw, Uncompressed RGB/YUV Video Streams Packet Processing

- RTP/UDP/IP Protocol Hardware Stack with separate releases: 10/100/1000 MbE; 10/25 GbE

- Targets raw, uncompressed RGB/YUV video streams. See DB-RTP-UDP-IP-NAL for H.264 NAL Streams

- Internet Protocol (IP) Packet Processor: IPv4 and IPv6 (optional) & ICMP (Internet Control Message Protocol) Protocol; IP header checksum generator (transmitter) & check (receiver), userselectable Maximum Transmission Unit (MTU), Unicast, Broadcast &Multicast Packet support; Compliance with IETF IPv4/IPv6 RFCs

-

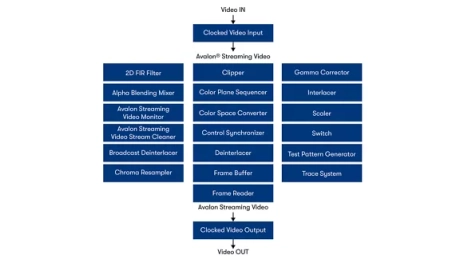

Video and Image Processing Pack

- Chroma Resampler

- Color Correction

- Color Filter Array Interpolation

- Gamma Correction