umc/ IP

Filter

Compare

3,084

IP

from

34

vendors

(1

-

10)

-

8MHz RC oscillator on UMC 55nm

- he present IP is a low dissipation and high precision relaxation oscillator

- And it is developed as a macro cell for clock generator

- It can generate a stable clock driven by 3.3v/1.2v power supply, which the typical out-frequency is about 8MHz.

-

Low-Speed 40KHz RC oscillator on UMC 55nm

- The present IP is a low power and low speed internal RC oscillator circuit (LSI RC OSC), used to drive the independent watchdog (IWDG) and the auto wakeup unit (AWU).

-

Low-Offset Programmable Gain Amplifier on UMC 55nm

- This present IP is applied to amplify the input signal with the programmable gain in Standalone/PGA mode or to work as a buffer in Follower mode, which operates in 1.8v~3.6v power supply and 1.2v power supply for control signals.

-

Integer-N PLL, 32M ~ 256MHz on UMC 55nm

- This present IP is a Phase Locked Loop (PLL) circuit

- It’s analog PLL suitable for various frequency node generations

- The VCO can run from 32MHz to 256MHz

- It contains input clock divider (DIVM), a feedback clock divider (DIVN) and level shifter block to switch signals between VDD12 and VDD33

-

Comparator with configurable hysteresis input on UMC 55nm

- This present IP is a comparator which is used to do the comparison between the different input groups, which operates in 3.3v power supply, the output of comparator is driven by 1.2v supply.

-

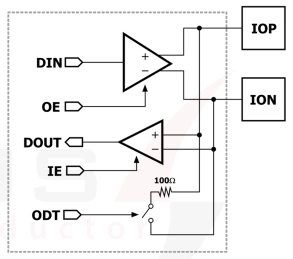

1.2V SLVS Transceiver in UMC 110nm

- This library delivers a compact and reliable 1.2V SLVS transceiver solution in UMC 110nm, optimized for high-speed, low-power applications.

- Featuring robust supply and ground noise rejection, 2kV HBM ESD protection, and integrated on die termination, this library provides both transmit and receive paths compliant with JESD8-13 SLVS standards at up to 200 Mbps.

-

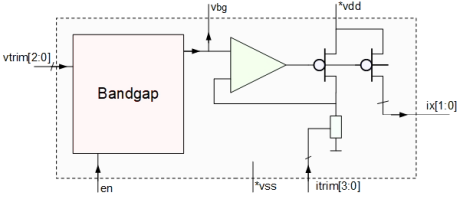

UMC 55nm ULP Bandgap / Current Reference

- 3σ 4% untrimmed voltage reference accuracy.

- 1% variation over -40ºC to 125ºC after trimming.

- 70dB low frequency PSRR.

- Trimmed, temperature compensated, 10µA reference current outputs with 3% accuracy.

- Trimmed IPTAT output currents can be provided.

- Less than 8µV noise from 0.1Hz to 10KHz.

-

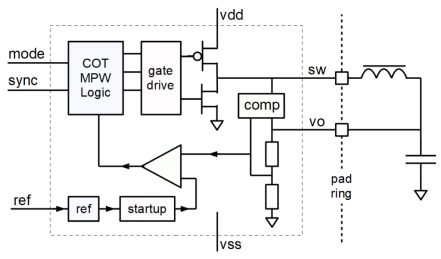

On-Chip IO to Core Voltage Buck Regulator on UMC 55nm ULP

- The OT1153 series on-chip regulators allow for efficient on-chip conversion of IO voltages to Core voltages.

- E.g. 3.3V to 1.2V with only one external inductor and one external capacitor.

- 2MHz conversion frequency is used to minimize the size of the external components. Input voltages of 2.5-5V are available and currents up to 80mA.

-

128x1 Bits OTP (One-Time Programmable) IP, UMC 0.18um 1.8V/5V BCD Process

- Fully compatible with UMC 0.18um 1.8V/5V BCD process

- Wide operating voltage range: 1.9-5.5V read voltage, 5.5V+/-5% program voltage

- High speed: 10µs program time per bit

- Wide temperature range: -40°C to 125°C for read and 25°C (i.e. room temp) for program