eSPI Controller IP

Filter

Compare

4

IP

from

4

vendors

(1

-

4)

-

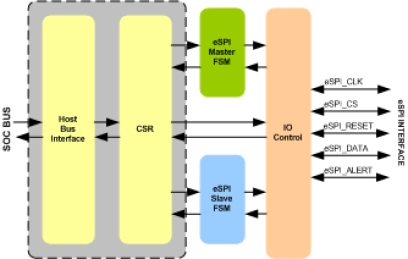

eSPI Controller IIP

- Compliant with eSPI base specification as defined in Enhanced Serial Peripheral Interface (eSPI) Specification rev.1.0.

- Supports addendum 0.7

- Supports Master and Slave Modes

- Supports Single, Dual and Quad modes

-

Express Serial Peripheral Interface IP Core

- Compliant with eSPI base specification as defined in Enhanced Serial Peripheral Interface (eSPI) Specification rev.1.0.

- Supports Master and Slave Modes

- Supports Single, Dual and Quad modes

- Supports TX and RX operation as per specs

-

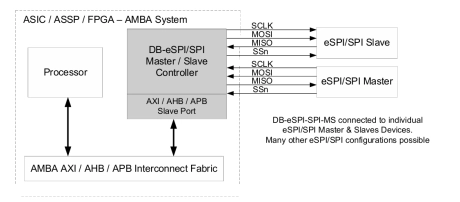

Enhanced SPI Controller IP- Master/Slave, Parameterized FIFO, AMBA APB / AHB / AXI Bus. Supports eSPI Master & Slave and SPI Master & Slave functions

- The DB-eSPI-SPI-MS-AMBA is a Serial Peripheral Interface (SPI) Controller Verilog IP Core supporting the addition of Enhanced SPI (eSPI) bus transfers to the standard SPI Master/Slave Controller. The DB-eSPI-SPI-MS contains an AMBA AXI, AHB, or APB Bus Interface for interfacing a microprocessor to external eSPI or SPI Master/Slave devices.

- The DB-eSPI-SPI-MS contains both eSPI and SPI Master and Slave functions.

-

Enhanced Serial Peripheral Interface – Master/Slave with single, dual, and quad eSPI Bus support for Intel CPU’s

- Rapid prototyping and time-to-market reduction

- Design risk elimination

- Development costs reduction