Xiphera IP

Filter

Compare

34

IP

from

1

vendors

(1

-

10)

-

-

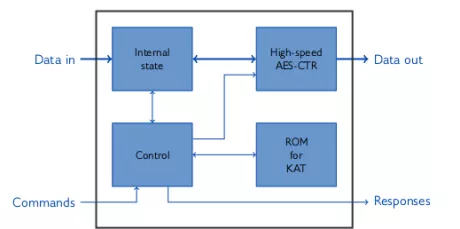

Pseudo Random Number Generator, high-speed version (AES256_CTR_DRBG)

- Fully digital design

- Portable to any ASIC or FPGA technology

- Fully standard compliant

-

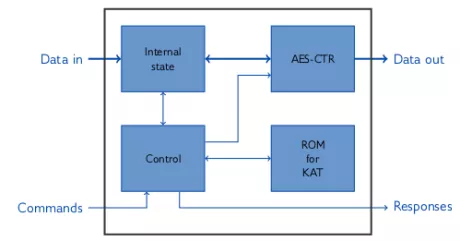

Pseudo Random Number Generator, balanced version (AES256_CTR_DRBG)

- Balanced Between Speed and Resource Requirements: XIP8103B can achieve over 2 Gbps throughput, while consuming only about 4000 Lookup Tables (LUTs) in a typical FPGA implementation.

- Versatility: XIP8103B supports the forward prediction resistance mode, which can be set on and off between output generation, as well as the use of personalization strings and additional inputs for instantiation and reseeding.

- Standard Compliance: XIP8103B is compliant with the NIST SP800-90A specification.

- XIP8103B can be combined with Xiphera’s NIST SP800-90Bcompliant XIP8001B to form a NIST SP800-90C compliant Random Bit Generator (RBG).

-

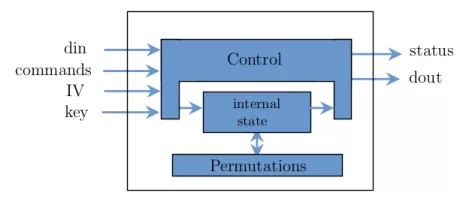

Ascon, A Lightweight Cryptographic Suite for AEAD and Hashing

- Small Resource Requirements

- Versatile Algorithm Support

- Secure Architecture

-

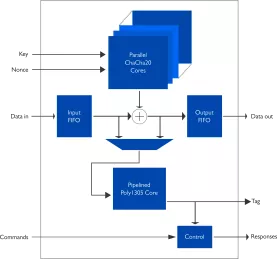

Balanced IP Core for ChaCha20-Poly1305 Authenticated Encryption

- Moderate resource requirements

- Performance

- High Throughput with Short Latency

-

High-Speed IP Core for ChaCha20-Poly1305 Authenticated Encryption

- Moderate resource requirements

- Performance

- High Throughput with Short Latency

-

AES-XTS, Advanced Encryption Standard (256-bit key), XTS mode IP Core

- Moderate resource requirements: The entire XIP1183H requires 28456 Adaptive Lookup Modules (ALMs) (Intel Agilex F), and does not require any multipliers or DSPBlocks. Contact sales@xiphera.com for ASIC resource requirements.

- Performance: XIP1183H achieves an impressive throughput in the tens of Gbps range, for example 43.48+ Gbps in Xilinx Versal Prime.

- Standard Compliance: XIP1183H is compliant with both the Advanced Encryption Algorithm (AES) standard, and the XTS standard.

- Optional Ciphertext stealing support as defined in IEEE Std 1619-2018.

-

AES-XTS, Advanced Encryption Standard (256-bit key), XTS mode IP Core

- Moderate resource requirements

- Performance

- Standard Compliance

-

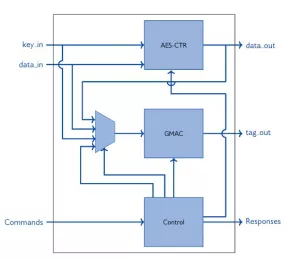

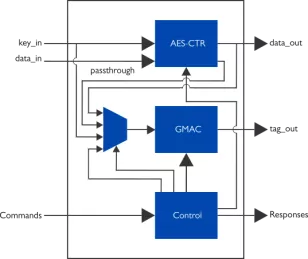

AES-GCM, Advanced Encryption Standard (256-bit key), Galois Counter Mode IP Core

- Moderate resource requirements: The entire XIP1111H requires approximately 21700 Adaptive Lookup Modules (ALMs) (Intel ® Cyclone ® V), and does not require any multipliers, DSPBlocks or internal memory in a typical FPGA implementation. Contact sales@xiphera.com for ASIC resource requirements.

- Optimized Implementation utilizing unrolling, pipelining, optimized AES S-box design, and GMAC calculation based on pipelined Karatsuba multipliers enable extremely high performance.

- Performance: XIP1113H achieves a throughput in the tens of Gbps range, for example 65+ Gbps in Xilinx ® UltraScale+ MPSoC.

- Standard Compliance: XIP1113H is fully compliant with both the Advanced Encryption Algorithm (AES) standard, as well as with the Galois Counter Mode (GCM) standard.

-

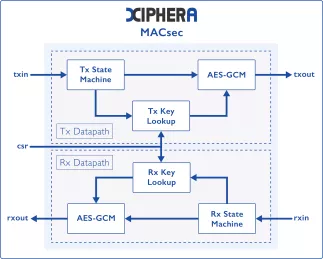

AES-GCM, Advanced Encryption Standard (256-bit key), Galois Counter Mode IP Core

- Compact resource requirements: The entire XIP1113B requires less than 2800 Adaptive Lookup Modules (ALMs) (Intel® Cyclone®V), and does not require any multipliers, DSPBlocks or internal memory in a typical FPGA implementation. Contact sales@xiphera.com for ASIC resource requirements.

- Performance: Despite its compact size, XIP1113B achieves a throughput in the Gbps range, for example 2.0 Gbps in Xilinx® Artix®-7 family.

- Standard Compliance: XIP1113B is fully compliant with both the Advanced Encryption Algorithm (AES) standard, as well as with the Galois Counter Mode (GCM) standard.

- Test Vector Compliance: XIP1111B passes all test vectors specified in MACsec GCM-AES Test Vectors.