WLAN IP

Filter

Compare

16

IP

from

12

vendors

(1

-

10)

-

SiGe BiCMOS WLAN Power Amplifier

- Linear Gain around 26 dB

- High PAE, High Linearity

- Maximum Linear Output Power in the range of 24dBm

-

802.11i CCM (CTR+CBC) AES Core for WiFi WLAN

- 8,900 ASIC gates at 802.11a/g OFDM data speeds

- Completely self-contained: does not require external memory

- Includes encryption, decryption, key expansion and data interface

- Support for Counter Mode Encryption (CTR) operation and CCM extensions (Counter Mode with CBC MAC, AES0CTR per NIST SP800-38C)

-

802.11a Physical Layer Baseband

- Fully IEEE 802.11a standard compliant

- Support for all data rates 6-54 Mbit/s

- Available as Verilog source code without vendor specific IP cores

- Synthesis possible for Altera and Xilinx FPGAs without source code changes

-

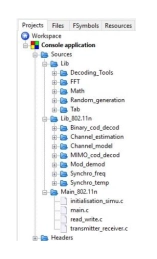

802.11ax PHY Layer C Floating-Point Code IP for the STA mode

- This IP includes a recommendation-compliant 802.11ax PHY layer C floating-point code for the Station (STA) mode.

- The code is integrated into a simulation environment that allows the configuration of mandatory features and the performance evaluation in terms of frame error rate.

- It is designed to generate fixed-point sequences in order to accelerate the development of both C fixed-point code and HDL code for prototyping environments.

-

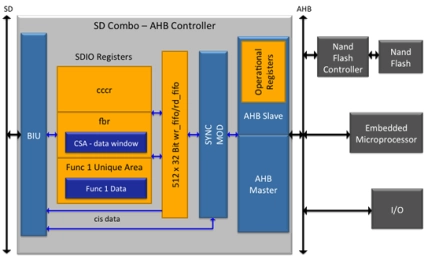

SD Card / SDIO Card Combo Device IP

- SD / SDIO Card Combo Device IP core is SD memory controller and a SDIO controller with an AHB interface.

- Combining with the optional NAND Flash Controller IP, the SD/SDIO Combo Device IP provides an integrated SD memory Card solution for designs that utilize NAND flash memory.

-

IEEE 802.11n/ac/ax Encoder and Decoder

- Fully synchronous design, using single clock

- Fully synthesizable drop-in module for FPGAs

- Optimized for high performance and low resources

- Low implementation loss

-

IEEE802.11n/ac/ax Wi-Fi LDPC Decoder and Encoder

- Layered decoding

- Soft decision decoding

- IEEE 802.11n/ac/ax standard compliant

- Support all LDPC code rates (½, 2/3 , ¾, and 5/6 )

- Support all LDPC codeword sizes(648, 1296, and 1944 bits)

-

Digital Communications (incl 5G)

- High processing power

- Customizable hardware

- Optimal algorithm mapping

- User defined quantization

-

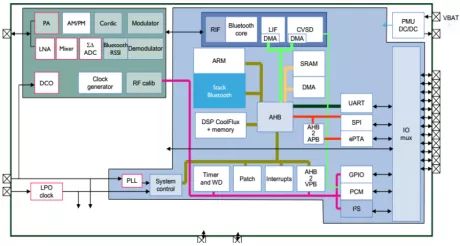

Bluetooth Dual Mode v4.2 RF Transceiver IP

- TSMC40nm

- High Volume Silicon Proven

- Extracted from Design Data Base of production chip

- Integrated balun

-

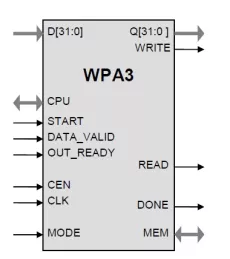

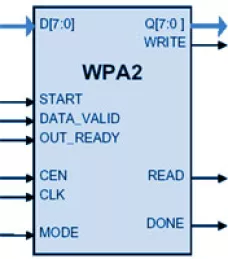

802.11i CCMP/TKIP IP Core

- Implementation of the WLAN security standard (802.11i) requires the NIST standard AES cipher in CTR and CBC modes (a.k.a. CCM) for encryption and message authentication with the CCMP protocol and RC4/”Michael” cipher for the TKIP.

- The WPA3 core is tuned for high data rate 802.11i applications (up to 2 Gbps for the CCMP protocol for 802.11n/802.11ac).