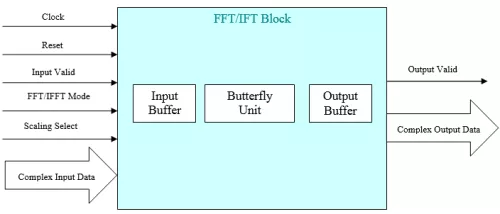

The Fast Fourier Transform (FFT) is an efficient algorithm for computing the Discrete Fourier Transform (DFT). This Intellectual Property core was designed to offer very fast transform times while keeping the resource utilization to a minimum. Our implementation is a radix-2 architecture. This core is written in VHDL, capable of being used on any FPGA/ASIC architecture. The FFT/IFFT core is able to perform an N-point FFT/IFFT in approximately 2.4xN clock cycles. It implements a double buffered input stage allowing a block to be processed while another block is being written in. Signal scaling is controllable by the Scaling Select configuration parameter. It can be either unscaled, scaled by 2 on every stage or optimised scaling. This core is implemented using a mix of parallel and serial processing for efficient resource utilisation and fast transform times.

N-Point FFT/IFFT

Overview

Key Features

- Parameterisable FFT block size

- Parameterisable input signal width

- Parameterisable internal scaling type (unscaled, scaled on every stage, optimised scaling)

- Programmable input and output word lengths and internal precision

- Area efficient design

- Silicon verified in multiple devices

- Optimized for WLAN (802.11, 802.16), DVB and other OFDM standards

Block Diagram

Deliverables

- Netlist or synthesizable RTL source code in VHDL

- Comprehensive verification test bench and vectors in VHDL

- Integration documentation and user guide

Technical Specifications

Short description

N-Point FFT/IFFT

Vendor

Vendor Name

Availability

now