Vector Graphics IP

Filter

Compare

18

IP

from

6

vendors

(1

-

10)

-

High-performance and low-power 2D vector graphics IP core

- K3000 is an OpenVG 1.1 compliant 2D vector graphics IP core that achieves the industry’s highest-level PPA (Power / Performance / Area), realizing smooth 2D vector drawing in combination with Qt and various font engines compliant with OpenVG 1.1.

-

Vector Graphics IP

- Display Resolution: Up to 4K

- ROPS (Pixels Per Cycle) : 1

- API Support:Vector Graphics VGLite API

- Embedded Linux Support

-

Vector Graphics IP core supporting OpenVG1.1 subset

- ant200 is a 2D vector graphics IP core that achieves further miniaturization by removing the texture function from the K3000 compliant with OpenVG 1.1.

-

2.5D GPU IP Core - API Support: Vector Graphics, VGLite API

- Embedded Linux support

- Pixel Rate (Pixel/Cycle): 1

- Display Resolution: up to 4K

- API Support: Vector Graphics, VGLite API

-

2D (vector graphics) & 3D GPU IP A GPU IP combining 3D and 2D rendering features with high performance, low power consumption, and minimum CPU load

- Pixel performance

- 3D rendering

- Texture size

- 2D rendering

-

2D (vector graphics) GPU IP Further advanced architecture for minimized CPU load and increased pixel performance in vector processing

- Pixel performance

- Texture size

- 2D rendering

-

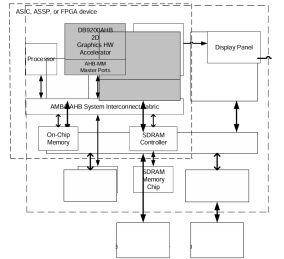

2D Graphics Hardware Accelerator (AHB Bus)

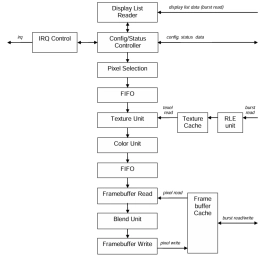

- Generates bitmaps from graphics instructions as well as combining existing bitmaps on and off-screen using one of 256 Raster Operations. A Raster Operation (ROP) is a bitwise Boolean operation (such as AND, OR, XOR, NOT) which lay the foundation for power hardware graphics primitive operations

- Generates characters from compressed bitmaps using its FONT Bitmap Color Expansion Unit

- Performs Alpha Blend operations of bitmaps with its Alpha Blend unit

- Draws lines, polygons, circles using its hardware efficient & pixel accurate Bresenham Algorithm Line Drawing Unit

-

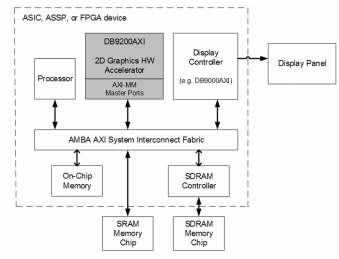

2D Graphics Hardware Accelerator (AXI Bus)

- Generates bitmaps from graphics instructions as well as combining existing bitmaps on and off-screen using one of 256 Raster Operations. A Raster Operation (ROP) is a bitwise Boolean operation (such as AND, OR, XOR, NOT) which lay the foundation for power hardware graphics primitive operations

- Generates characters from compressed bitmaps using its FONT Bitmap Color Expansion Unit

- Performs Alpha Blend operations of bitmaps with its Alpha Blend unit

- Draws lines, polygons, circles using its hardware efficient & pixel accurate Bresenham Algorithm Line Drawing Unit

-

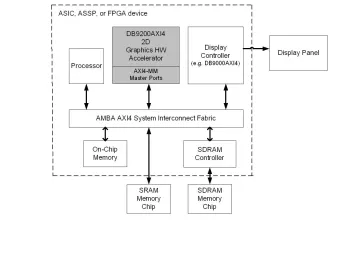

2D Graphics Hardware Accelerator (AXI4 Bus)

- Generates bitmaps from graphics instructions as well as combining existing bitmaps on and off-screen using one of 256 Raster Operations. A Raster Operation (ROP) is a bitwise Boolean operation (such as AND, OR, XOR, NOT) which lay the foundation for power hardware graphics primitive operations

- Generates characters from compressed bitmaps using its FONT Bitmap Color Expansion Unit

- Performs Alpha Blend operations of bitmaps with its Alpha Blend unit

- Draws lines, polygons, circles using its hardware efficient & pixel accurate Bresenham Algorithm Line Drawing Unit

-

2D GPU Hardware IP Core

- D/AVE 2D is a 2D GPU Hardware IP Core, optimized for easy integration into FPGAs and ASICs.

- Focus of D/AVE 2D is to provide cost efficient high quality vector graphics with subpixel processing and an extended anti-aliasing functionality.