VESA Display IP

Filter

Compare

82

IP

from

23

vendors

(1

-

10)

-

VESA Display Stream Compression (DSC) IP Core

- Supports Versions 1.1, 1.2 and 1.2a

- Supports RGB and YCbCr color spaces

- 1-to-8 slice support

-

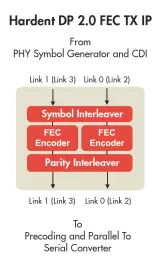

VESA DisplayPort 1.4 Forward Error Correction (FEC) Transmitter

- VESA DisplayPort 1.4 compliant

- Reed-Solomon RS (254,250) FEC, 10-bit symbols

- Two-way interleaving for 1-, 2- and 4-lane modes (4-lane mode requires 2 FEC IP core instances)

- DisplayPort main 8b/10b encoder included (Tx only)

- Status and control can be done with signals or optionally via an integrated APB register module (Rx)

-

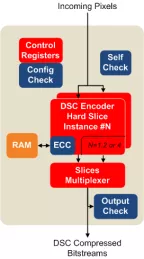

VESA DSC 1.1 Encoder IP Core for Automotive Displays (ASIL-B Ready ISO 26262 Certified)

- VESA DSC 1.1 compliant

- Supports all DSC 1.1 mandatory encoding mechanisms

- Configurable maximum display resolution

-

MIPI DSI-2 controllers with VESA DSC for high-speed serial interface between application processor and displays

-

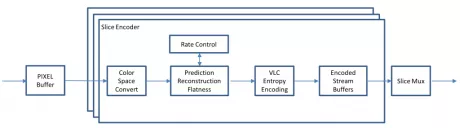

VESA DSC V1.2 Encoder

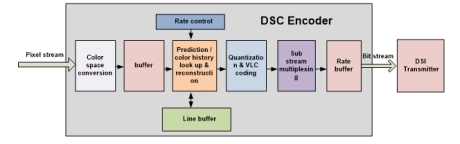

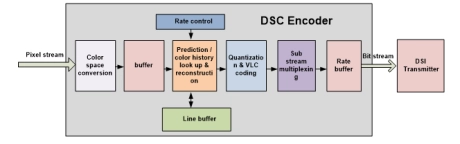

- VESA introduced the first Display Stream Compression (DSC) standard in 2014. The DSC 1.1 has been incorporated into the VESA Embedded DisplayPort (eDP) and MIPI® DSI embedded mobile interface standards. The latest VESA Display Compression-M (VDC-M) standard has also been adopted into the MIPI DSI standard. For mobile applications, DSC 1.1 and VDC-M mainly serve to reduce the video interface data rate, which reduces system power, prolongs battery life, and reduces interconnects to enable sleeker designs. For external display interfaces, DSC 1.2b extends resolution across existing connectors and cables, enabling 8K video and legacy support from the same connection.

- Being compliant with the VESA DSC 1.2a and 1.2b standards, the IP core supports various prediction schemes (MMAP, BP, MPP, ICH) as well as color formats in YCbCr and RGB. It transfers more pixel data over display links to save memory size in embedded frame buffers in display driver ICs and performs visually lossless compression, low gate count and latency for ultra-high-definition display applications. It can be easily integrated into ASIC and FPGA applications.

- Programmable display resolutions

-

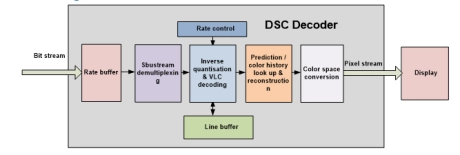

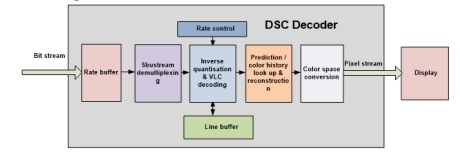

VESA DSC V1.2 Decoder

- Being compliant with the VESA DSC 1.2a and 1.2b standards, the IP core supports various prediction schemes (MMAP, BP, MPP, ICH) as well as color formats in YCbCr and RGB.

- It transfers more pixel data over display links to save memory size in embedded frame buffers in display driver ICs and performs visually lossless compression, low gate count and latency for ultra-high-definition display applications.

-

VESA DSC V1.2 Encoder

- Being compliant with the VESA DSC 1.2a and 1.2b standards, the IP core supports various prediction schemes (MMAP, BP, MPP, ICH) as well as color formats in YCbCr and RGB.

- It transfers more pixel data over display links to save memory size in embedded frame buffers in display driver ICs and performs visually lossless compression, low gate count and latency for ultra-high-definition display applications. It can be easily integrated into ASIC and FPGA applications.

-

VESA DSC V1.2 Decoder

- Being compliant with the VESA DSC 1.2a and 1.2b standards, the IP core supports various prediction schemes (MMAP, BP, MPP, ICH) as well as color formats in YCbCr and RGB.

- It transfers more pixel data over display links to save memory size in embedded frame buffers in display driver ICs and performs visually lossless compression, low gate count and latency for ultra-high-definition display applications. It can be easily integrated into ASIC and FPGA applications.

-

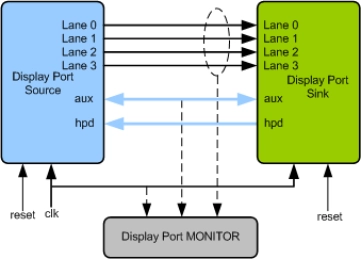

Display Port 2.0 Verification IP

- Full Display port 2.0 source device and sink device functionality.

- Supports backward compatibility with previous versions upto DPv1.4a

- Supports multi lanes upto 4 lanes.

- Supports control symbols for framing.

-

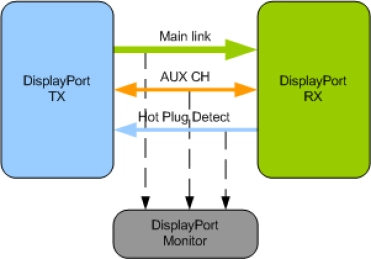

Display Port Verification IP

- Full Display port source device and sink device functionality.

- Display port supports version 1.0,1.1,1.2,1.2a,1.3,1.4,1.4a and 2.0 specification.

- Supports multi lanes upto 4 lanes.

- Supports control symbols for framing(Both Default & Enhanced framing mode).