USB 3.0 SSIC Bridge IP

Filter

Compare

1

IP

from

1

vendors

(1

-

1)

-

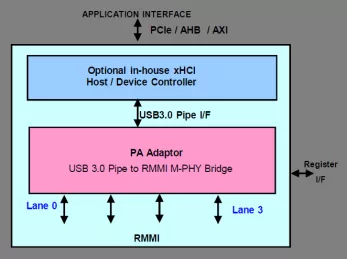

USB 3.0 SSIC Controller

- Compliant with SSIC v1.01

- Compliant with M-PHY Specification v2.0

- Compliant with USB3.0 Pipe Specification