USB 3.0 SSIC IP

Filter

Compare

6

IP

from

4

vendors

(1

-

6)

-

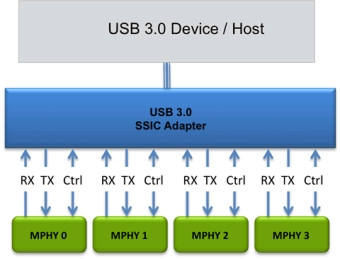

USB 3.0 SSIC Adapter

- Compliant with SSIC specification 1.0

- Compliant with MIPI-MPHY (Type-1) specification Rev 3.0-r.03

- Interfaces to the USB3 Device/Host controller via the standard PIPE3 interface at 8/16/32-bit data widths

-

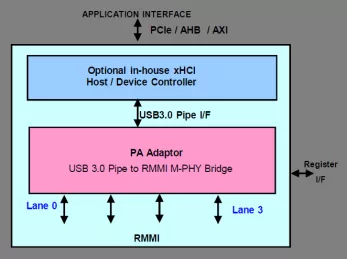

USB 3.0 SSIC Controller

- Compliant with SSIC v1.01

- Compliant with M-PHY Specification v2.0

- Compliant with USB3.0 Pipe Specification

-

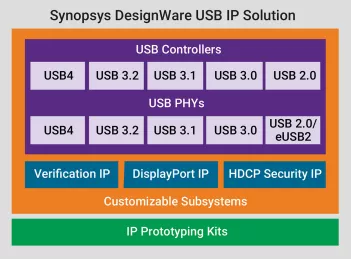

SuperSpeed USB 3.0 Host Controller Supporting SSIC and HSIC

- Supports SuperSpeed USB power savings modes, Uniform Power Format (UPF) and dual power rails

- Lowers overall system power by design

- Configurable data buffering options to fine-tune performance/area trade-offs

- Host supports SuperSpeed, High-Speed, Full-Speed, and Low-Speed operation

-

SuperSpeed USB 3.0 Device Controller Supporting SSIC and HSIC

- Supports SuperSpeed USB power savings modes, Uniform Power Format (UPF) and dual power rails

- Lowers overall system power by design

- Configurable data buffering options to fine-tune performance/area trade-offs

- Host supports SuperSpeed, High-Speed, Full-Speed, and Low-Speed operation

-

SuperSpeed USB 3.0 Dual Role Device Controller, Configurable for SSIC and HSIC

- Supports SuperSpeed USB power savings modes, Uniform Power Format (UPF) and dual power rails

- Lowers overall system power by design

- Configurable data buffering options to fine-tune performance/area trade-offs

- Host supports SuperSpeed, High-Speed, Full-Speed, and Low-Speed operation

-

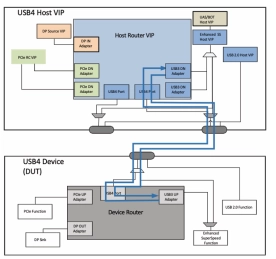

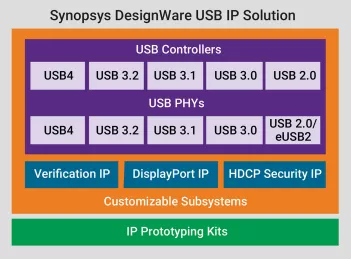

Verification IP for USB

- Avery VIP for USB is a comprehensive solution for verification of USB-based designs ranging from the USB 2.0, 3.x, and 4.0 standards, including xHCI host controllers and USB mass storage class standards for UAS and BOT.

- USB VIP allows users to verify their designs by developing custom tests at several levels of abstraction.