UDP IP IP

Filter

Compare

84

IP

from

30

vendors

(1

-

10)

-

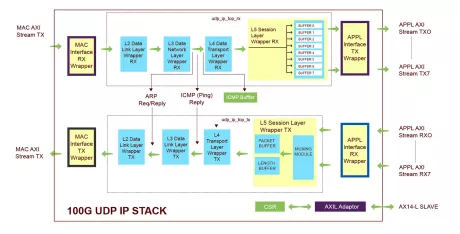

100G UDP IP Stack

- 100G Ethernet

- IPv4 support without packet fragmentation

- Jumbo Frames

- Transmit and Receive

- ARP with Cache

- ICMP (Ping Reply) UDP Unicast

-

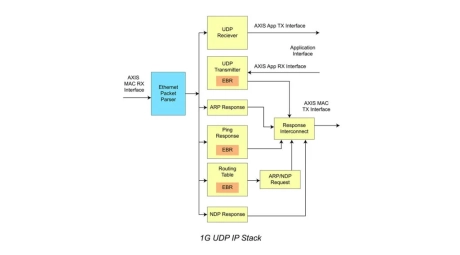

1G UDP IP Stack

- Supports 1G Ethernet packet processing.

- UDP Port Filtering based on port numbers.

- Address Resolution Protocol (ARP) is supported.

- IP Header Checksum Validation.

-

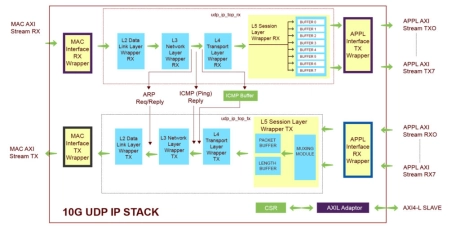

10G UDP IP Stack

- 10G Ethernet

- IPv4 support without packet fragmentation

- Jumbo Frames

- Transmit and Receive

- ARP with Cache

- ICMP (Ping Reply)

-

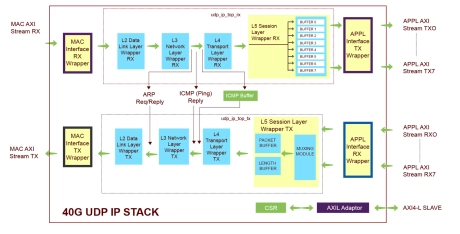

40G UDP IP Stack

- 40G Ethernet

- IPv4 support without packet fragmentation

- Jumbo Frames

- Transmit and Receive

-

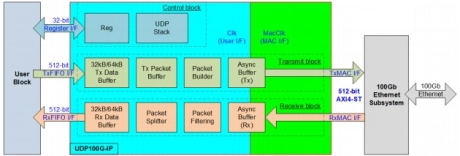

UDP 100G / 40G / 25G / 10G / 1G IP core

- UDP100G/40G/25G/10G/1G IP core is the epochal solution implemented without CPU.

- This IP core is suitable for network application.

- This IP product includes reference design for AMD FPGA. It helps you to reduce development time.

-

UDP Offload Engine for IPv6

- Full IPv6 support including Echo, NDP, MLD

- Line-rate UDP/IPv6 transmit and receive

- RFC 768 & RFC 8200 compliant

- Packet parsing and header synthesis in hardware

-

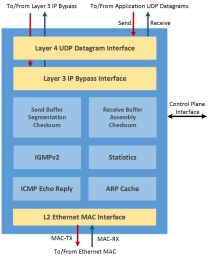

UDP Offload Engine for IPv4

- The UDP/IP core implements the UDP/IPv4 standard RFC 768/791, including checksum, segmentation and reassembly hardware offload.

- The UDP/IP core is tested for operation with popular FPGA vendors’ GbE Ethernet MACs.

-

Ethernet IP Core compliant with 100BASE-TX and 1000BASE-T

- The Ethernet IP Core is compliant with 100BASE-TX and 1000BASE-T, supporting all commonly used PHY interfaces like MII, GMII, RGMII and SGMII.

- Thanks to its built-in DMA capabilities and the wide variety of high-speed interfaces (AXI/AXI Lite and AHB/APB bus), the IP Core can be coupled with a microprocessor to handle TCP/IP packets.

-

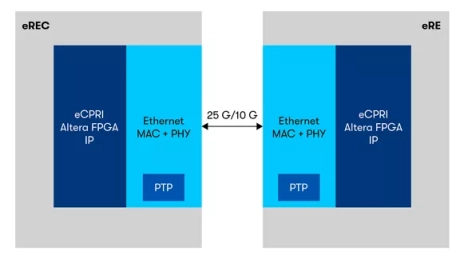

eCPRI Altera® FPGA IP

- The enhanced Common Public Radio Interface (eCPRI) Altera® FPGA IP core implements the eCPRI specification version 2.0

- It is a front-haul interface protocol for radio base stations aimed at connecting the eCPRI Radio Equipment Control (eREC) and the eCPRI Radio Equipment (eRE) via front-haul transport network.

-

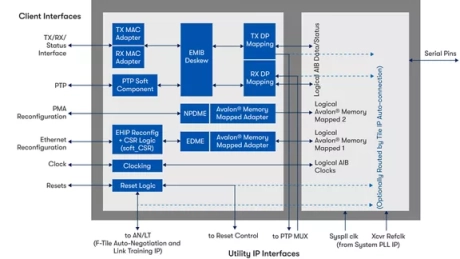

Intel® Agilex™ 7 F-Tile Ethernet Hard IP

- The Intel® Agilex™ 7 FPGA F-Tile incorporates a fracturable, configurable, hardened Ethernet protocol stack for supporting rates from 10G to 400G, compatible with IEEE 802.3 specification, and other related Ethernet Consortium specifications.