UALink IP

Filter

Compare

10

IP

from

4

vendors

(1

-

10)

-

UALink Controller

- The UALink Controller, part of Cadence’s verified UALink IP subsystem, delivers ultra-low latency and high-bandwidth interconnects that enable seamless scale-up connectivity between AI accelerators. I

- t supports memory semantics for read, write, and atomic operations, ensuring fast, coherent data handling across workloads. UALink IP provides a scalable, future-ready solution for next-generation AI infrastructure.

-

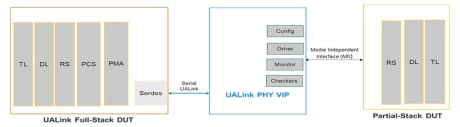

Simulation VIP for UALink

- The Ultra Accelerator Link (UALink) Verification IP (VIP) provides a complete bus functional model (BFM) with integrated automatic protocol checks for physical layer in addition to Media Independent Interface (MII).

- Designed for easy integration in testbenches at IP, SoC, and system levels, the VIP helps engineers reduce time to first test, accelerate verification closure, and ensure end-product quality.

-

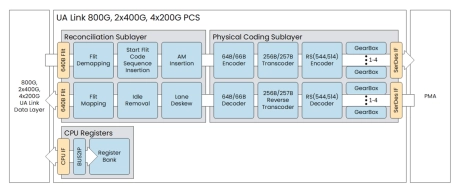

UALink PCS IP Core

- The UA Link PCS IP Core is a high-performance, silicon-agnostic and fully compliant Physical Coding Sublayer (PCS) implementation of UALink_200 specification.

- Designed for seamless integration into accelerator, switch, and SoC designs, it delivers deterministic low-latency, robust error correction, and compatibility with multiple high-speed Ethernet-derived link rates.

-

224G SerDes PHY and controller for UALink for AI systems

- UALink, the standard for AI accelerator interconnects, facilitates this scalability by providing low-latency, high-bandwidth communication.

- As a member of the UALink Consortium, Cadence offers verified UALink IP subsystems, including controllers and silicon-proven PHYs, optimized for robust performance in both short and long-reach applications and delivering industry-leading power, performance, and area (PPA).

-

UALink IP Solution

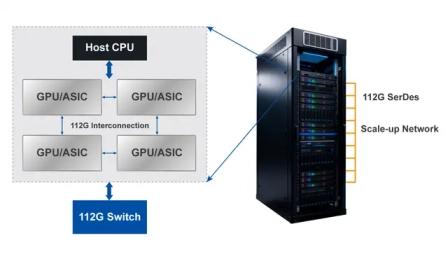

- Lightweight, low latency IP solution for XPU to XPU interconnects optimized for AI workloads

- Fully integrated IP solution for AI accelerators (XPUs), GPUs, and switches

- Enables maximum throughput with up to 200Gbps per lane

- Supports memory sharing capabilities to expand compute and memory resources from XPU to XPU

-

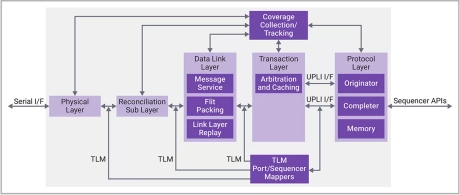

Verification IP for UALink

- API based transaction flow for ease of use

- Specification linked Protocol checks and functional coverage

- Exceptions, callback, error injection and analysis ports for Scoreboard

- TLM ports at each layer for traffic tracing

- Configurable timers for threshold testing

-

UALinkSec Security Module

- UALink 200 v1.0 / UALinkSec specification support

- Plug and play with Synopsys UALink controller

- Supports 200 GT/s per lane, enabled by silicon-proven Synopsys 224G PHY IP

- Support bifurcation of up to 4 ports

-

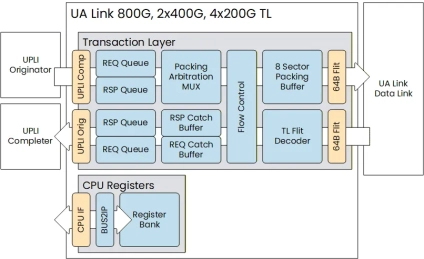

UA Link TL IP core

- UALink_200 Specifi cation Compliant: Implements TL functions per Rev 1.0

- Multi-Rate Support : 200 GBASE-KR1/CR1, 400 GBASE-KR2/CR2, 800 GBASE-KR4/CR4

- Atomic Operations, Authentication tags, Cache Synchronization, Flow Control

-

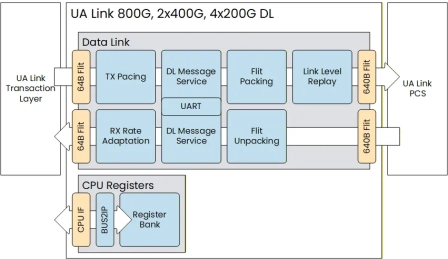

UA Link DL IP core

- The UA Link DL IP Core is a high-performance, silicon-agnostic and fully compliant Data Layer implementation of UALink_200 specifi cation.

- Designed for seamless integration into accelerator, switch, and SoC designs, it delivers deterministic low-latency, robust error correction, and compatibility with multiple high-speed Ethernet-derived link rates.

-

112G Multi-SerDes

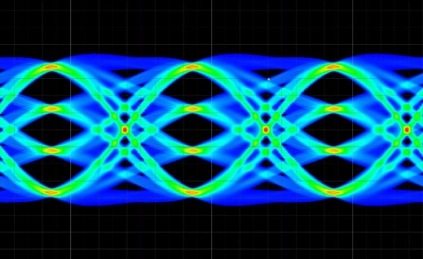

- Designed with a small footprint, ultra-low latency, and low power consumption, the 112G SerDes maximizes bidirectional memory access efficiency, reduces software complexity, and helps chip developers leverage existing Ethernet infrastructure to significantly lower Total Cost of Ownership (TCO).

- Featuring IEEE 802.3-compliant Forward Error Correction (FEC), 35dB ultra-high channel loss compensation, and adaptive high-speed equalization technologies (CTLE, FFE), it provides full-cycle link protection—from error correction to pre-warning—enabling highly compatible, stable, and efficient chip-to-chip connectivity solutions.