TSMC N5 IP

Filter

Compare

191

IP

from

5

vendors

(1

-

10)

-

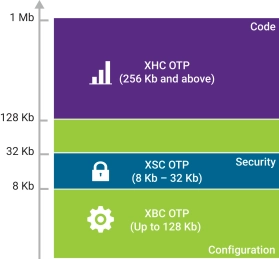

NVM OTP XBC TSMC N5 1.2V

- Designers face the challenge of creating secure, cost-effective, low power, and reliable SoC designs

- Synopsys’ embedded one-time programmable (OTP) non-volatile memory (NVM) IP, based on XHF architecture, enables designers to address these challenges

- Synopsys’ OTP NVM IP architecture provides high levels of security, high yields, low power, and excellent reliability, which is why Synopsys OTP NVM is the leader in antifuse technology with >10B units shipped and availability in more than a dozen foundries

- Synopsys OTP NVM IP is silicon-verified in TSMC N4P, N5, N5A, N6, and N7

-

LPDDR6/5X/5 PHY V2 - TSMC N5

- The LPDDR6/5X/5 PHY IP enables ASICs, ASSPs, system-on-chips (SoCs), and system-in-package applications requiring high-performance LPDDR6, LPDDR5X, and/or LPDDR5 SDRAM interfaces operating at up to 14.4 Gbps

- With flexible configuration options, the LPDDR6/5X/5 PHY IP can be used in a variety of applications supporting LPDDR6, LPDDR5X, and/or LPDDR5 SDRAMs, precisely targeting the specific power, performance, and area (PPA) requirements of these systems

- LPDDR6 SDRAM’s combination of high bandwidth, capacity, low power, and cost effectiveness makes LPDDR6/5X/5 SDRAMs an attractive solution for traditional and new markets

- The LPDDR6/5X/5 PHY IP is designed to appeal to a variety of applications including: * Traditional mobile environments * Consumer products * Automotive solutions * Artificial intelligence * Data center applications

-

TSMC N5 1.2V/1.5V/1.8V GPIO Platform MS Add-on

- Synopsys’ General-Purpose I/O (GPIO) Library IP provides designers with the input/output operation, functionality, and reliability required for their SoCs targeting mobile, automotive, and high-performance computing (HPC) applications

- The IP is silicon-proven and available in several foundries and process technologies from 3nm to 22nm

- Synopsys GPIO library is designed to support multiple voltages; it offers a complete set of support cells (supply, corner spacers, diode breakers, terminators) required to create complete I/O pad rings for system-on-chips (SoCs)

- The library is compatible with flip-chip packaging

-

TSMC N5 1.2V/1.5V/1.8V GPIO Platform

- Synopsys’ General-Purpose I/O (GPIO) Library IP provides designers with the input/output operation, functionality, and reliability required for their SoCs targeting mobile, automotive, and high-performance computing (HPC) applications

- The IP is silicon-proven and available in several foundries and process technologies from 3nm to 22nm

- Synopsys GPIO library is designed to support multiple voltages; it offers a complete set of support cells (supply, corner spacers, diode breakers, terminators) required to create complete I/O pad rings for system-on-chips (SoCs)

- The library is compatible with flip-chip packaging

-

TSMC N5 1.2V/1.8V GPIO Platform MS Add-on

- Synopsys’ General-Purpose I/O (GPIO) Library IP provides designers with the input/output operation, functionality, and reliability required for their SoCs targeting mobile, automotive, and high-performance computing (HPC) applications

- The IP is silicon-proven and available in several foundries and process technologies from 3nm to 22nm

- Synopsys GPIO library is designed to support multiple voltages; it offers a complete set of support cells (supply, corner spacers, diode breakers, terminators) required to create complete I/O pad rings for system-on-chips (SoCs)

- The library is compatible with flip-chip packaging

-

TSMC N5 1.2V/1.8V GPIO Library with 1.8V Failsafe MS add on

- Synopsys’ General-Purpose I/O (GPIO) Library IP provides designers with the input/output operation, functionality, and reliability required for their SoCs targeting mobile, automotive, and high-performance computing (HPC) applications

- The IP is silicon-proven and available in several foundries and process technologies from 3nm to 22nm

- Synopsys GPIO library is designed to support multiple voltages; it offers a complete set of support cells (supply, corner spacers, diode breakers, terminators) required to create complete I/O pad rings for system-on-chips (SoCs)

- The library is compatible with flip-chip packaging

-

TSMC N5 1.2V/1.8V GPIO Library with 1.8V Failsafe

- Synopsys’ General-Purpose I/O (GPIO) Library IP provides designers with the input/output operation, functionality, and reliability required for their SoCs targeting mobile, automotive, and high-performance computing (HPC) applications

- The IP is silicon-proven and available in several foundries and process technologies from 3nm to 22nm

- Synopsys GPIO library is designed to support multiple voltages; it offers a complete set of support cells (supply, corner spacers, diode breakers, terminators) required to create complete I/O pad rings for system-on-chips (SoCs)

- The library is compatible with flip-chip packaging

-

TSMC N5 1.2V/1.8V GPIO Platform

- Synopsys’ General-Purpose I/O (GPIO) Library IP provides designers with the input/output operation, functionality, and reliability required for their SoCs targeting mobile, automotive, and high-performance computing (HPC) applications

- The IP is silicon-proven and available in several foundries and process technologies from 3nm to 22nm

- Synopsys GPIO library is designed to support multiple voltages; it offers a complete set of support cells (supply, corner spacers, diode breakers, terminators) required to create complete I/O pad rings for system-on-chips (SoCs)

- The library is compatible with flip-chip packaging

-

TSMC N5 1.2V/1.8V/2.5V GPIO Library with 2.5V Failsafe

- Synopsys’ General-Purpose I/O (GPIO) Library IP provides designers with the input/output operation, functionality, and reliability required for their SoCs targeting mobile, automotive, and high-performance computing (HPC) applications

- The IP is silicon-proven and available in several foundries and process technologies from 3nm to 22nm

- Synopsys GPIO library is designed to support multiple voltages; it offers a complete set of support cells (supply, corner spacers, diode breakers, terminators) required to create complete I/O pad rings for system-on-chips (SoCs)

- The library is compatible with flip-chip packaging

-

TSMC N5 1.2V/1.8V SD/eMMC IO MS Add-on

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards