SuperSpeed USB 10 Gbps IP

Filter

Compare

60

IP

from

2

vendors

(1

-

10)

-

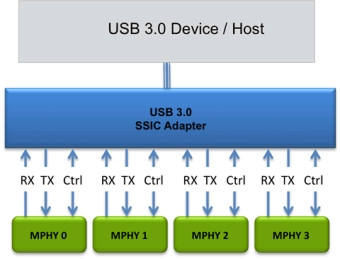

USB 3.0 SSIC Adapter

- Compliant with SSIC specification 1.0

- Compliant with MIPI-MPHY (Type-1) specification Rev 3.0-r.03

- Interfaces to the USB3 Device/Host controller via the standard PIPE3 interface at 8/16/32-bit data widths

-

USB 3.1 PHY (10G/5G) - TSMC N5 x1 OTG, North/South Poly Orientation

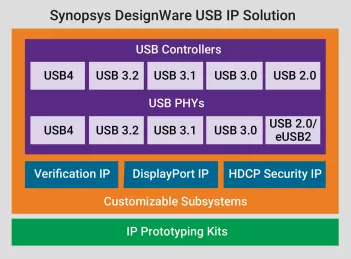

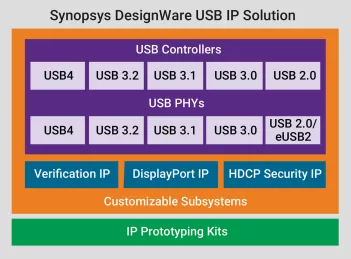

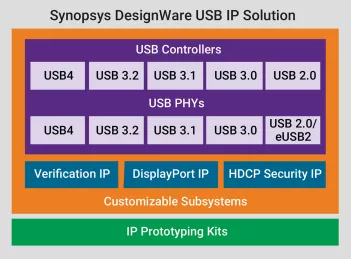

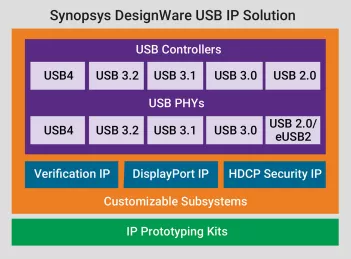

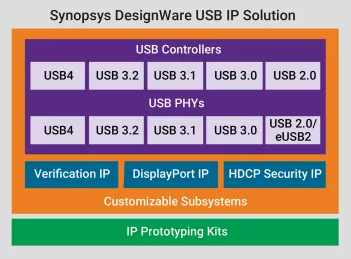

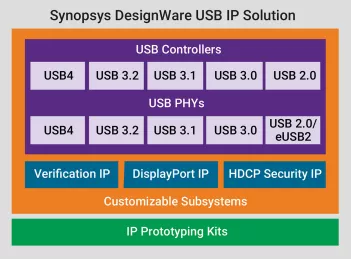

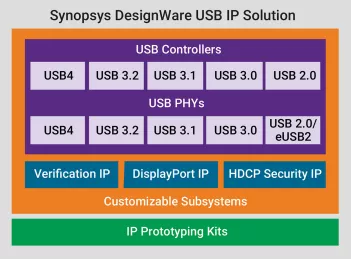

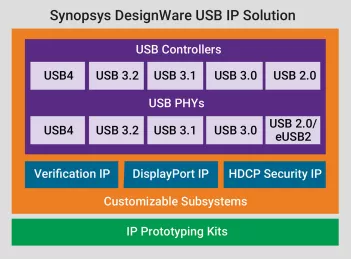

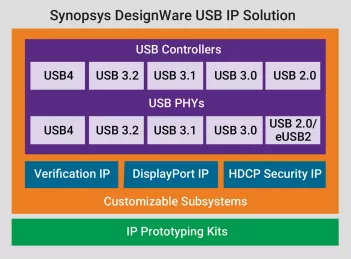

- Part of a complete IP solution including xHCI host and device controllers, PHYs, verification IP, 1 IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C 3.1 PHY IP supports USB Type-C specification

- Supports the SuperSpeedPlus (10 Gbps) and SuperSpeed (5 Gbps) speed modes

-

USB 3.1 PHY (10G/5G) - TSMC N3P X1 OTG, North/South Poly Orientation

- Part of a complete IP solution including xHCI host and device controllers, PHYs, verification IP, 1 IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C 3.1 PHY IP supports USB Type-C specification

- Supports the SuperSpeedPlus (10 Gbps) and SuperSpeed (5 Gbps) speed modes

-

USB 3.1 PHY (10G/5G) - TSMC N3A x1 OTG, North/South Poly Orientation for Automotive AEC-Q100 Grade 2

- Part of a complete IP solution including xHCI host and device controllers, PHYs, verification IP, 1 IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C 3.1 PHY IP supports USB Type-C specification

- Supports the SuperSpeedPlus (10 Gbps) and SuperSpeed (5 Gbps) speed modes

-

USB 3.1 PHY (10G/5G) - TSMC 7FF x1 OTG, North/South Poly Orientation

- Part of a complete IP solution including xHCI host and device controllers, PHYs, verification IP, 1 IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C 3.1 PHY IP supports USB Type-C specification

- Supports the SuperSpeedPlus (10 Gbps) and SuperSpeed (5 Gbps) speed modes

-

USB 3.1 PHY (10G/5G) - TSMC 6FF x1 OTG, North/South Poly Orientation

- Part of a complete IP solution including xHCI host and device controllers, PHYs, verification IP, 1 IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C 3.1 PHY IP supports USB Type-C specification

- Supports the SuperSpeedPlus (10 Gbps) and SuperSpeed (5 Gbps) speed modes

-

USB 3.1 PHY (10G/5G) - TSMC 16FFC x1 OTG, North/South Poly Orientation

- Part of a complete IP solution including xHCI host and device controllers, PHYs, verification IP, 1 IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C 3.1 PHY IP supports USB Type-C specification

- Supports the SuperSpeedPlus (10 Gbps) and SuperSpeed (5 Gbps) speed modes

-

USB 3.1 PHY (10G/5G) - TSMC 16FF+LL x1 OTG, North/South Poly Orientation

- Part of a complete IP solution including xHCI host and device controllers, PHYs, verification IP, 1 IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C 3.1 PHY IP supports USB Type-C specification

- Supports the SuperSpeedPlus (10 Gbps) and SuperSpeed (5 Gbps) speed modes

-

USB 3.1 PHY (10G/5G) - TSMC 16FF+GL x1 OTG, North/South Poly Orientation

- Part of a complete IP solution including xHCI host and device controllers, PHYs, verification IP, 1 IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C 3.1 PHY IP supports USB Type-C specification

- Supports the SuperSpeedPlus (10 Gbps) and SuperSpeed (5 Gbps) speed modes

-

USB 3.1 PHY (10G/5G) - TSMC 12FFC x1 OTG, North/South Poly Orientation

- Part of a complete IP solution including xHCI host and device controllers, PHYs, verification IP, 1 IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C 3.1 PHY IP supports USB Type-C specification

- Supports the SuperSpeedPlus (10 Gbps) and SuperSpeed (5 Gbps) speed modes