Still Image Codec IP

Filter

Compare

11

IP

from

4

vendors

(1

-

10)

-

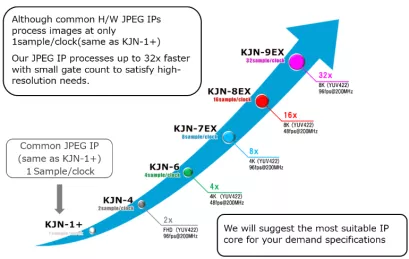

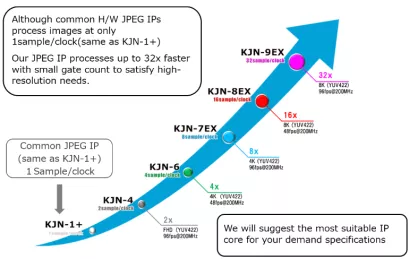

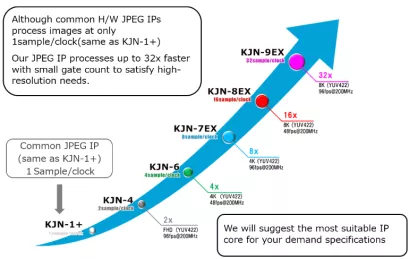

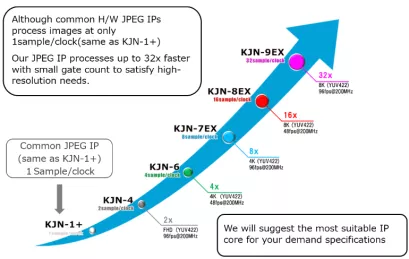

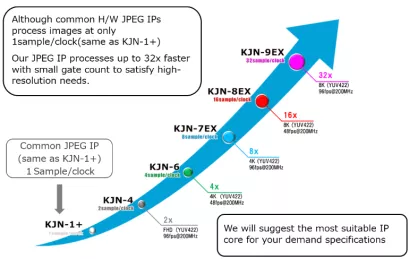

JPEG Codec Full HD(YUV422) 30fps@126MHz(1Sample/clk)

- The arithmetic accuracy satisfies the requirement of compliance testing of JPEG Part2 (ISO/IEC10918-2).

- Image Data I/O Format:Block Interleaved Format.

- Image Size:Any size that can be divided by MCU unit.

- Operation mode like processing mode, image size, DRI value etc. are set in internal register via external CPU.

-

-

JPEG Codec 8K(YUV422) 48fps@200MHz,

- ?Based on JPEG Extended DCT-based process/Baseline process Standards.

- ?The arithmetic accuracy also satisfies the requirement of compliance testing of JPEG Part2 ?ISO/IEC10918-2?j.

- ?Image Data I/O Format:Block Interleaved Format

- ?Image Size:Any size that can be divided by MCU unit.

-

JPEG Codec 4K(YUV422) 96fps@200MHz, (8Sample/clk)

- The arithmetic accuracy satisfies the requirement of compliance testing of JPEG Part2 (ISO/IEC10918-2).

-

JPEG Codec 4K(YUV422) 48fps@200MHz. (4Sample/clk)

- The arithmetic accuracy satisfies the requirement of compliance testing of JPEG Part2 (ISO/IEC10918-2).

- Image Data I/O Format:Block Interleaved Format.

- Image Size:Any size that can be divided by MCU unit.

- Operation mode like processing mode, image size, DRI value etc. are set in internal register via external CPU.

-

JPEG Codec Full HD(YUV422) 48fps@100MHz. (2Sample/clk)

- The arithmetic accuracy satisfies the requirement of compliance testing of JPEG Part2 (ISO/IEC10918-2).

- Image Data I/O Format:Block Interleaved Format.

- Image Size:Any size that can be divided by MCU unit.

- Operation mode like processing mode, image size, DRI value etc. are set in internal register via external CPU.

-

JPEG Codec Full HD(YUV422) 24fps@100MHz.(1sample/clk)

- •The arithmetic accuracy satisfies the requirement of compliance testing of JPEG Part2 (ISO/IEC10918-2).

- • Image Data I/O Format:Block Interleaved Format.

- • Image Size:Any size that can be divided by MCU unit.

- • Operation mode like processing mode, image size, DRI value etc. are set in internal register via external CPU.

-

JPEG Codec 4K(YUV422) 96fps@200MHz,

- ?Based on JPEG Extended DCT-based process/Baseline process Standards.

- ?The arithmetic accuracy also satisfies the requirement of compliance testing of JPEG Part2 ?ISO/IEC10918-2?j.

- ?Image Data I/O Format:Block Interleaved Format

- ?Image Size:Any size that can be divided by MCU unit.

-

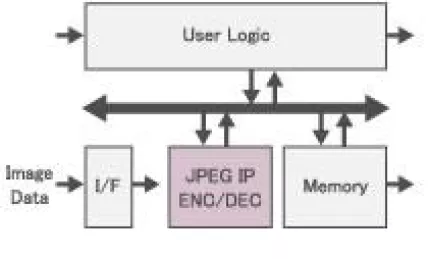

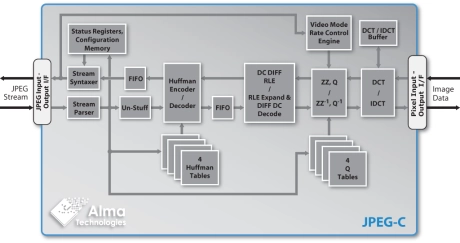

8-bit Baseline JPEG Codec with Optional Video Rate Control

- The JPEG-C core is a standalone and high-performance, half-duplex 8-bit Baseline JPEG Codec for still image and video compression applications.

- Full compliance with the Baseline Sequential DCT mode of the ITU-T T.81 JPEG standard makes this IP core ideal for interoperable systems and devices.

- The JPEG-C is available for ASIC or AMD-Xilinx, Efinix, Intel, Lattice and Microchip FPGA and SoC based designs.

-

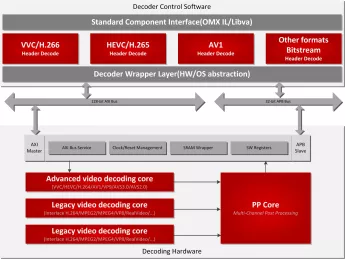

Microprocessor IP for video codecs and video processing -- High Number of Streams Decoder For Data Center

- Enables up to 256 streams decoding with robustness, high throughput single-core solution, or multi-core solution, supporting VVC, AV1, HEVC, H.264, AVS3, AVS2, VP9 video formats, JPEG, and legacy formats.