SpaceWire IP

Filter

Compare

11

IP

from

5

vendors

(1

-

10)

-

SpaceWire IP core

- The SpaceWire IP core is compliant with the IEEE 1355 standard. It is capable of 100Mbps full duplex bitrate.

- Support for FreeRTOS, RTEMS and Linux is available, a TCP/IP networking driver is provided for Linux.

-

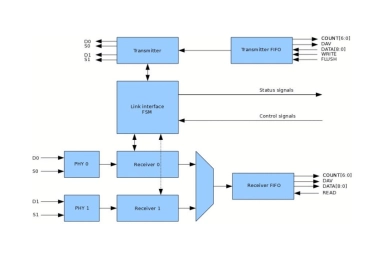

SpaceWire CODEC

- The GRSPW_CODEC core implements a SpaceWire encoder-decoder with a 9-bit wide FIFO host interface in each direction. The core complies to the SpaceWire standard (ECSS-E-ST-12C).

- Data is transmitted and received through 9-bit wide FIFOs with configurable depth. The core also provides an interface for transmitting and receiving Time-codes as well as configuring the link properties such as the link rate.

-

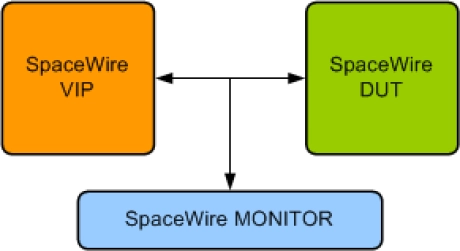

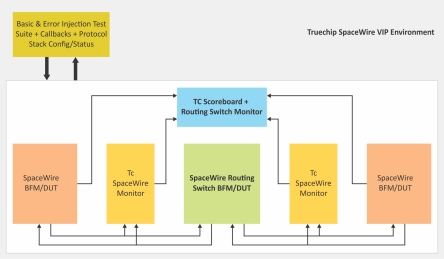

SpaceWire Verification IP

- Compliant with ECSS E‐ST‐50‐12C Standard.

- Supports speeds between 2 Mb/s and 400 Mb/s.

- Supports sending packets of information from a source node to a specified destination node.

- Supports full-duplex point-to-point serial data communication links.

-

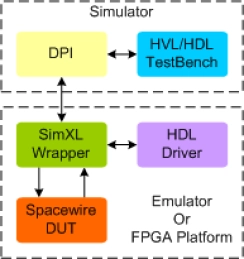

SpaceWire Synthesizable Transactor

- Supports ECSS E‐ST‐50‐12C Standard

- Supports speeds between 2 Mb/s and 400 Mb/s

- Supports Full SpaceWire Functionality

-

SpaceWire Verification IP

- Available in UVM, System Verilog.

- Compliant to Specification ECSS-E-ST-50-12 C rev 1.

- Supports speeds between 2Mb/s to 400Mb/s

- Supports full duplex Serial data communication links

-

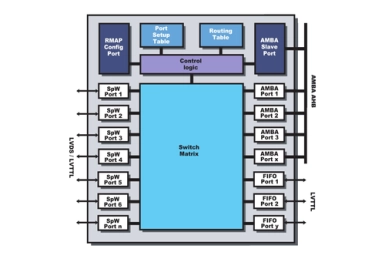

SpaceWire Router

- The SpaceWire router IP core supports all mandatory and optional features in the ECSS-E-ST-50-12C. It supports from 2 to 31 ports in addition to the mandatory configuration port.

- Each port (except the configuration port) can be individually configured to be SpaceWire links, FIFO interfaces or AMBA interfaces.

- The AMBA ports are limited to a maximum of 16 in a single router. The configuration port provides an RMAP target (ECSS-E-ST-50-52C), and an optional AMBA AHB slave interface, both used for accessing internal configuration and status registers. The SpaceWire Plug-and-Play (PnP) protocol can optionally be supported on the configuration port.

-

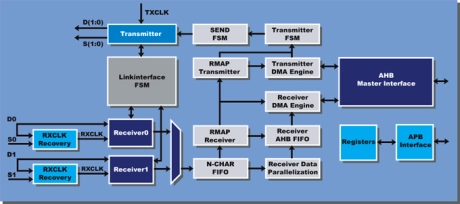

SpaceWire link controller with SpaceWire RMAP support and AMBA host interface

- Full implementation of Spacewire standard

- Protocol ID extension ECSS-E-50-12 part 2

- Optional RMAP protocol draft C

- AMBA AHB back-end with DMA

-

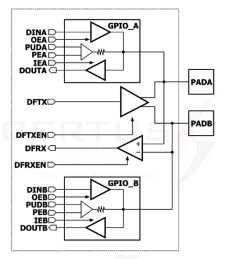

Rad-Hard GPIO, ODIO & LVDS in SkyWater 90nm

- This Library, developed on SkyWater 90nm CMOS, delivers a radiation-hardened suite of robust interfaces covering general-purpose, open-drain, and high-speed differential signaling needs.

- The GPIO provides reliable 3.3V digital I/O up to 150 MHz with JESD8C.01 compliance, built-in pull-ups/downs, and 2 kV HBM protection.

-

CCSDS ECSS

- The CCSDS/ECSS Spacecraft Data Handling IP cores represent a collection of cores that have been developed specifically for the space sector.

- These IP cores implement functions commonly used in spacecraft data handling and management systems. Supporting Software Libraries and EGSE equipment are available.

-

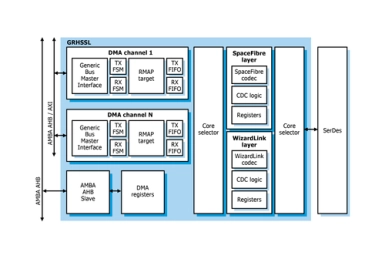

SpaceFibre and WizardLink Interface

- SpaceFibre codec designed according to the SpaceFibre specification ECSS-E-ST-50-11C, single-lane implementation

- WizardLink codec designed to interface with Texas Instrument TLK2711 transceiver

- The IP can inter-operate with off-chip SerDes devices or with FPGA/ASIC hard macros

- Optional 8b10b encoding