SRAM Compiler on TSMC 28nm IP

Filter

Compare

1

IP

from

1

vendors

(1

-

1)

-

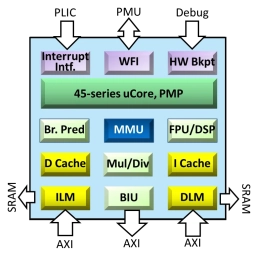

8-stage superscalar RISC-V processor

- The 64-bit AX45 is an 8-stage superscalar processor that supports RISC-V specification, including “G” (“IMAFD”) standard instructions, “C” 16-bit compression instructions, “P” Packed-SIMD/DSP instructions, “B” bit manipulation, and Andes performance enhancements, plus Andes Custom Extension™ (ACE) for user-defined instructions.