SPI4.2 IP

Filter

Compare

6

IP

from

3

vendors

(1

-

6)

-

SPI4.2

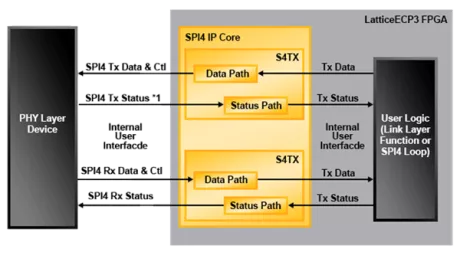

- The Soft SPI4 IP core is fully compliant with the OIF System Packet Interface Level 4 Phase 2 Revision 1 (SPI4.2.1) interface standard

- Supported through Diamond or ispLEVER IPexpress™ tool for easy user configuration and parameterization

- Supports up to 256 independent channels

- 400 to 500MHz DDR Dynamic mode operation in LatticeSC and LatticeSCM devices

-

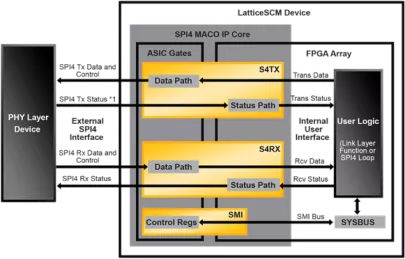

SPI 4.2 MACO Core

- Fully compliant with OIF-SPI4.02.0 Specification

- Supports up to 256 logical ports

- 700 Mbps operation in Static Mode

- 1+ Gbps operation in Dynamic Mode

-

INTERLAKEN IIP

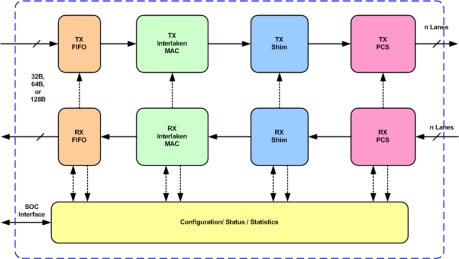

- Compliant with Interlaken protocol specification v1.2

- Interlaken look as side protocol 1.1

- Interlaken retransmission extension specification 1.2

- Interlaken Reed-Solomon Forward Error Correction Extension 1.1

-

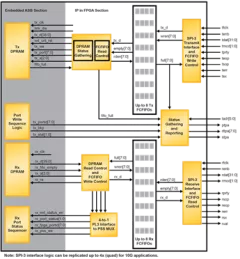

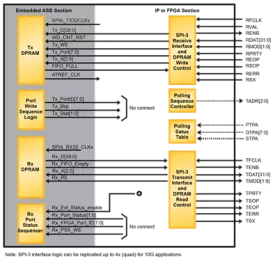

Quad SPI-3 to SPI-4 PHY Layer Bridge

- Complete Quad SPI-3 to SPI-4 PHY Layer Bridge Solution Based on the ORCA ORSPI4 FPSC

- IP Targeted to the ORSPI4 Programmable Array Section Implements Functionality Conforming to OIF-SPI3-01.0, Including:

- SPI-4 Functionality Supported by the Embedded Section of the ORSPI4, Including:

-

Quad SPI-3 to SPI-4 Link Layer Bridge

- Complete Quad SPI-3 to SPI-4 Link Layer Bridge Solution Based on the ORCA ORSPI4 FPSC

- IP Targeted to the ORSPI4 Programmable Array Section. Implements Functionality Conforming to OIF-SPI3-01.0, Including:

- SPI-4 Functionality Supported by the Embedded Section of the ORSPI4, Including:

-

SPI-4 Phase 2 Interface Solutions

- Up to 700 MHz DDR on SPI-4.2 interface supporting 1.2 Gbps pin pair total bandwidth

- Supports Static and Dynamic Phase Alignment utilizing ChipSync™ technology

- Bandwidth optimized source core achieves optimal bus throughput without additional FPGA resources

- Flexible clocking options utilizing DCM, PMCD, global, and regional clocking resources