SHA-256 IP

Filter

Compare

35

IP

from

24

vendors

(1

-

10)

-

SHA-256 IP

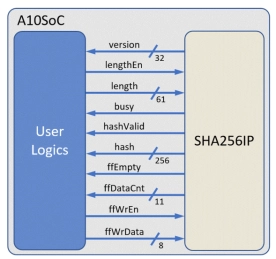

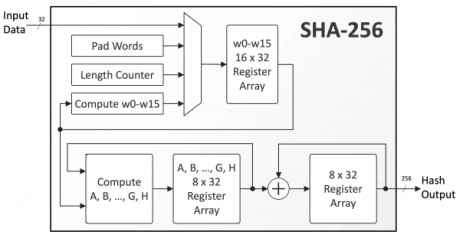

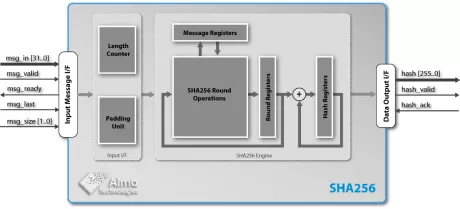

- SHA-256 IP is an optimized and efficient implementation of a secure hash algorithm SHA-256 specified in FIPS 180-4 standard. SHA256-IP can process 512-bit data blocks in just 65 clock cycles.

- Delivering 7.875Mbps throughput per 1MHz clock such as 2.362 Gbps throughput @ 300MHz.

-

-

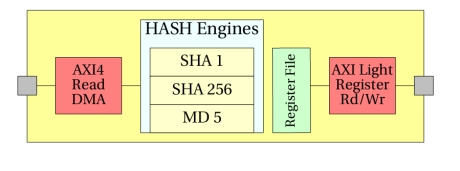

HASH Core, providing MD5, SHA1 and SHA256. Includes DMA and AXI Interface

- This is a high performance, small footprint HASH IP Core. It supports three HASH algorithms: MD5, SHA1, SHA256. A S/G DMA engine keeps the core running.

- Each hash engine has it’s own dedicated clock, which is independent of the main AXI clock.

-

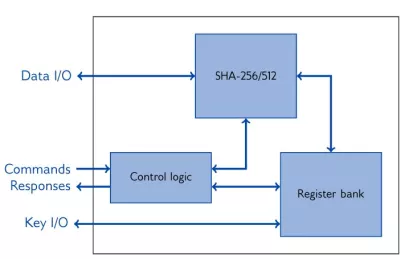

HKDF/HMAC/SHA-256/SHA-512, SHA-256 IP Core with Extended Functionalities

- Versatility

- Constant Latency

- Compact Size

-

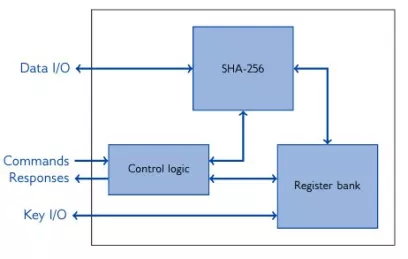

HKDF/HMAC/SHA-256, SHA-256 IP Core with Extended Functionalities

- Versatility

- Constant Latency

- High Performance

-

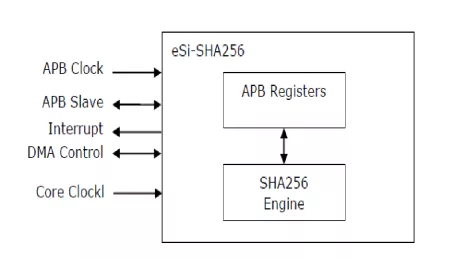

SHA256 & SHA224 core

- Simple register based interface

- 65 clock cycles per 512 bits of input data

- AMBA 3 APB slave interface

- DMA flow-control interface

-

256-bit SHA Secure Hash Crypto Engine

- The SHA-256 encryption IP core is a fully compliant implementation of the Message Digest Algorithm SHA-256. It computes a 256-bit message digest for messages of up to (264 – 1) bits.

- Developed for easy reuse in ASIC and FPGA applications, the SHA-256 is available optimized for several technologies with competitive utilization and performance characteristics.

-

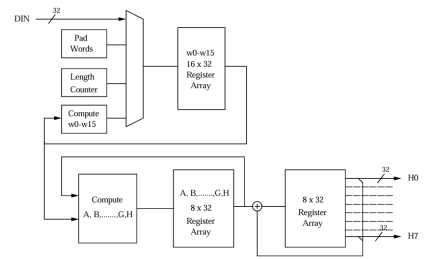

SHA-256 and SHA-224

- One clock per step algorithm implementation.

- Automatic pad insertion.

- Handles byte-aligned messages from zero up to 2^^40 bytes in length.

- Direct Message Digest output, with strobe.

-

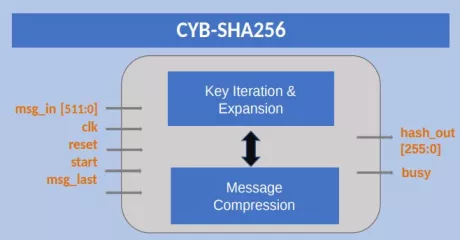

SHA-256 Secure Hash Function

- Compliant to FIPS 180-2 specification of SHA-256.

- Bit padding internally implemented.

- Supports 2^64-1 bits maximum message length.

- Supports input message length multiple of 8-bit.

- Initial value of the chaining variables selected before synthesis.

-

SHA-256 Processor

- This core is a fully compliant implementation of the Message Digest Algorithm SHA-256. It computes a 256-bit message digest for messages of up to (264 – 1) bits. Simple, fully synchronous design with low gate count.

- The OL_SHA256 core is a fully compliant hardware implementation of the SHA-256 algorithm, suitable for a variety of applications.