Post-Quantum Cryptography Accelerator IP

Filter

Compare

9

IP

from

7

vendors

(1

-

9)

-

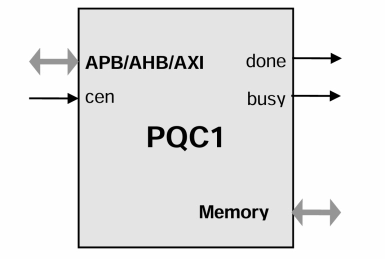

APB Post-Quantum Cryptography Accelerator IP Core

- Implements ML-KEM and ML-DSA post-quantum cryptography digital signature standards. The system interface is an microprocessor slave bus (APB, AHB, AXI options are available).

- The design is fully synchronous and requires only minimal CPU intervention due to internal microprogramming sequencer.

-

Post-Quantum Accelerator

- The Post-Quantum Cryptography IP core provides a high-efficiency hardware solution supporting ML-KEM (Kyber) and ML-DSA (Dilithium) as standardized in FIPS 203 and 204, along with additional hash-based signature schemes including SPHINCS+, XMSS, and LMS.

-

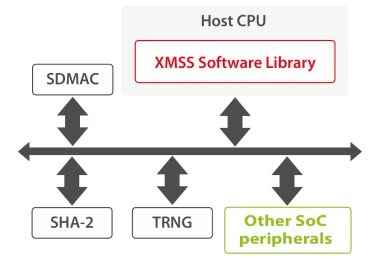

XMSS Post-Quantum Cryptography IP

- XMSS is a Post-Quantum Cryptographic (PQC) algorithm, meaning it is mathematically designed to be robust against a cryptanalytic attack using a quantum computer.

- XMSS is a stateful Hash-Based Signature Scheme that has been recommended by NIST in 2020.

-

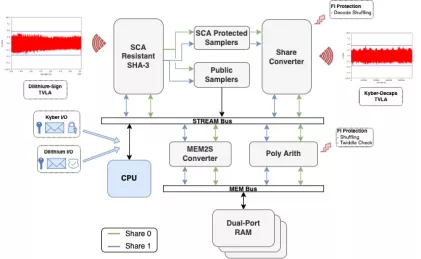

Unified Hardware IP for Post-Quantum Cryptography based on Kyber and Dilithium

- Turn-key implementations of the NIST FIPS recommended CRYSTALS post-quantum for key encapsulation (KEM) and digital signature algorithm (DSA)

-

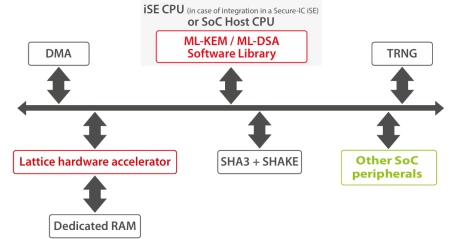

ML-KEM / ML-DSA Post-Quantum Cryptography IP

- ML-KEM (Crystals-Kyber) and ML-DSA (Crystals-Dilithium) are Post-Quantum Cryptographic (PQC) algorithms, meaning they are mathematically designed to be robust against a cryptanalytic attack using a quantum computer.

- Both have been standardized by the NIST in it post-quantum cryptography project.

-

Crypto Box Toolset Secure Accelerator

- The Hybrid Crypto Box IP core is a comprehensive, high-efficiency cryptographic solution that combines RSA, ECC, AES, and SHA-2/HMAC with a built-in accelerator for post-quantum algorithms such as ML-KEM (Kyber) and ML-DSA (Dilithium). Designed for embedded systems with balanced resource constraints, it enables secure key exchange, digital signatures, authenticated encryption, and hashing, future-proofed for the quantum era.

-

Agile PQC Public Key Accelerator

- Agile IP comprised of HW/FW/SW, adaptable to future standards’ evolution

- Highly configurable IP can be tuned for specific applications with most optimal PPA

- Scalable PQC PKA IP complies with latest NIST PQC algorithms

-

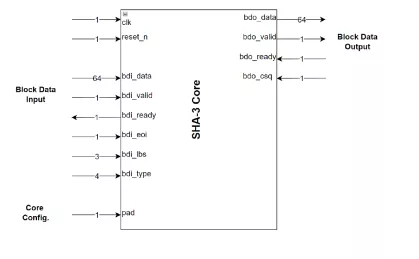

SHA3 core for accelerating NIST FIPS 202 Secure Hash Algorithm

- Supports variable length SHA-3 Hash Functions

- Supports Extendable Output Functions (XOF)

- Configurable architecture for achieving the required performance and silicon area

-

Cryptographic Cores IP

- The Cryptographic Cores IP portfolio delivers secure, high-performance implementations of symmetric, asymmetric, and post-quantum algorithms.

- Designed for low-area, low-latency operation, the silicon-proven cores help SoC designers and embedded teams build trusted, efficient devices for IoT, automotive, medical, and industrial markets.